Welcome to this first lecture on VHDL, a critical language in the world of hardware design. By the end of this lecture, you will understand VHDL's basic syntax and be able to write simple programs with text output.

#### HWMod WS24

#### VHDL Basics

Language Propert Identifiers Entity Architecture Process Packages Basic Operators Basic Expression Elements Control Flow Labels Example

# Hardware Modeling [VU] (191.011) - WS24 -

**VHDL Basics**

Florian Huemer & Sebastian Wiedemann & Dylan Baumann

WS 2024/25

Modified: 2025-03-30, 16:53 (e9b236f)

## └─VHDL Basics └─Introduction └─Introduction

VHCL (May High Speed Integrated Circuit Hardware Description Language)

Wildly used in induity and academia Marraites (Weigh Spearatic Cystem Weigh, ...

Lots of online resources available Takinala, books, took, ...

Desclayed in the SPS for ULS Description Desclayed in the SPS for ULS Description Reservices (May Boroly Description Reservices (May Boroly Description)

VHDL stands for Very High Speed Integrated Circuit Hardware Description Language. It is used to model electronic systems. VHDL is especially popular in industries where reliability and accuracy are crucial, such as aerospace, automotive, and telecommunications. You can find a lot of additional learning and discussion material online. We will also provide helpful resources and links on our TUWEL page. Let's start with some background information. VHDL was developed in the 80s by the U.S. Department of Defense and is based on Ada, which is known for its safety features and strong typing. The U.S. Department of Defense needed a way to specify hardware behavior, which natural language could not effectively capture.

|                                                                                                                                     | Introduction                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HWMod<br>WS24<br>VHDL Basics<br>Introduction<br>Language Properties<br>Identifiers<br>Entity<br>Architecture<br>Process<br>Packaoos | <ul> <li>VHDL (Very High Speed Integrated Circuit Hardware Description Language)</li> <li>Widely used in industry and academia</li> <li>Alternatives: Verilog, SystemC, System Verilog,</li> </ul> |

| Basic Operators<br>Basic Expression<br>Elements<br>Control Flow<br>Labels<br>Example                                                | <ul> <li>Lots of online resources available</li> <li>Tutorials, books, tools,</li> </ul>                                                                                                           |

|                                                                                                                                     | <ul> <li>Developed in the 80's for U.S. Department of Defense</li> <li>Based on Ada (strongly typed concept)</li> <li>Revisions 1987, 93, 2000 and 2002</li> </ul>                                 |

#### −VHDL Basics └─Introduction └─Introduction (cont'd)

Initially solely used to document hardware

Later avanced by perhatic location

Dely adaet of commonsk can be transferred

binderdere (synthesizable)

VHDL Standard 2008 taught in this locture

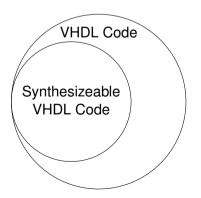

All VHDL code is simulatable

VHDL Standard 2008 taught in this locture

All the shares are supported

bits in the semified stadent in three from the for the

Initially, VHDL was used primarily for documenting hardware. The goal was to create a secure and robust way to describe hardware and catch errors early in the design process. VHDL allowed for a precise description of hardware components that manufacturers could use to build the desired equipment. Later, synthesis tools were developed to convert VHDL descriptions into actual hardware. This caused some VHDL features, such as specifying delays, to be not directly translatable into hardware and considered non-synthesizable. VHDL includes both synthesizable and non-synthesizable features. However, non-synthesizable VHDL code CAN be simulated. For instance a delay statement may not be synthesizable but in a simulation it can mimic real world signal delays. Anyway, this will be covered in more detail in future lectures. In this lecture, we'll cover basic VHDL syntax, so you can start writing simple software programs with terminal outputs with the help of a simulator. We'll focus on VHDL-2008, as it is the most widely supported standard with broad tool compatibility. Keep in mind that many tools default to older VHDL standards, so you might need to configure them to use VHDL-2008. Next, let's dive into the VHDL syntax.

# Introduction (cont'd)

#### HWMod WS24

VHDL Basics Introduction Language Properties Identifiers Entity Architecture Process Packages Basic Coparators Basic Expression Elementa Control Flow Labels Example

- Initially solely used to document hardware

- Later extended by synthesis tools

- Only subset of commands can be transferred to hardware (= synthesizable VHDL)

- All VHDL code is simulatable

- VHDL Standard 2008 taught in this lecture

- Attention: not all 2008 features are supported by EDA tools

- Has to be explicitly selected in tools (not the default)

Case insensitive variable = VARIABLE = VARIABLE

Let's start by looking at some fundamental properties of VHDL as a language. First, it's important to know that VHDL is a case-INsensitive language. This means that whether you type your identifiers and keywords in lowercase or uppercase, VHDL will treat them as the same.

# Language Properties

#### HWMod WS24

#### VHDL Basics Introduction Language Properties Identifiers Entity Architecture Process Packages Basic Operators Basic Depression Elements Control Flow Labels

Case insensitive variable = VARIABLE = VaRiAbLe

Another key aspect is that commands in VHDL are terminated by a semicolon, just like in Java or C.

# Language Properties

#### HWMod WS24

VHDL Basics Introduction Language Properties Udentifiers Entity Architecture Process Packages Basic Coparators Basic Expression Elements Control Flow Labels Example

- Case insensitive variable = VARIABLE = VaRiAbLe

- Commands terminated by ';'

Case Insensitive

variable = VARIABLE = VARIABLE

Commands terminated by '.

Comments

Comment

Since 2008 multi-like comments possible (\*\* and \*/)

Single-line comments are marked with two dashes. For multi-line comments, which were introduced in the 2008 revision, you can use the Java or C style multi line comment delimiters.

# Language Properties

#### HWMod WS24

/HDL Basics Introduction Language Properties Identifiers Entity Architecture Process Basic Operators Basic Expression Elements Control Flow Labels Example Case insensitive variable = VARIABLE = VaRiAbLe

Commands terminated by ';'

#### Comments

- '--' single line comment

- Since 2008 multi-line comments possible ('/\*' and '\*/')

Case interditive

Variable = VARIABLE = VARIABLE

Variable

Commands thermated by '

Commands

Company

Commands

Company

Commands

Commands

Command

Command

Throughout this course, you'll notice that we use specific formatting for keywords, data types, comments, and constants to make the code more readable. This will help you quickly identify different elements when you're reading VHDL code in our slides.

# Language Properties

#### HWMod WS24

VHDL Basics Introduction Language Properties Identifiers Entity Architecture Process Packages Basic Operators Basic Sperators Basic Sperators Elements Control Flow Labels Example

- Case insensitive variable = VARIABLE = VaRiAbLe

- Commands terminated by ';'

#### Comments

- '--' single line comment

- Since 2008 multi-line comments possible ('/\*' and '\*/')

- Format used in lecture

- keywords

- datatype

- comment

- CONSTANT

- everything else

#### −VHDL Basics └─Identifiers └─**Basic Identifiers**

Next, let's discuss identifiers in VHDL, which are names used for variables and various other elements in your code. This slide shows a BNF, or Backus-Naur Form, which is a notation used to describe the syntax of context-free grammars. We will frequently use this notation throughout the course to present the VHDL syntax. BNF is also used extensively in third-party resources, like the VHDL standard, to explain syntax rules. If you are not already familiar with BNF, I encourage you to get comfortable with it. In BNF, curly brackets indicate repetition, square brackets indicate optional elements, and vertical bars indicate choices between alternatives. If a term appears without any brackets, it is mandatory to use that term to form a valid syntax. As an example take the BNF for basic identifiers here. Identifiers must start with a letter, and there are certain restrictions you need to be aware of. For example, you cannot have underscores at the end of an identifier or two consecutive underscores within an identifier. Valid examples include left, left1, and left underscore 0. Invalid identifiers might include names like underscore left, 0 left, or any identifier that ends with an underscore.

## **Basic Identifiers** HWMod **WS24** basic\_identifier ::= letter{[underline]letter\_or\_digit} First character must be a letter Identifiers No underscore at the end No two consecutive underscores invalid valid left left left1 0left left left10

left\_0

left2\_0

#### 4

identifier := letter/[underline]letter or digit

First character must be a lette

No underscore at the end

No two consecutive un valio left left1 left1

## └─VHDL Basics └─Identifiers └─Extended Identifiers

Extended identifier syntax: extended\_identifier ::= /graphic\_character(graphic\_character)\

Special identifier enclosed by backslashes 281

In VHDL, we have a concept called extended identifiers. These are identifiers that are enclosed within backslashes. They allow us to use characters that aren't typically allowed in standard identifiers, like special characters, spaces, or even language-specific letters. You can check out the VHDL standard for a comprehensive naming method scheme.

# **Extended Identifiers**

#### HWMod WS24

#### VHDL Basics Introduction Language Properties Identifiers Entity Architecture Process Packages Basic Coperators Basic Expression Elements Control Flow Labels Example

- Extended identifier syntax:

- extended\_identifier ::=

\graphic\_character{graphic\_character}\

- Special identifier enclosed by backslashes

## └─VHDL Basics └─Identifiers └─Extended Identifiers

Function details grants

function for motion of yobass

function for motion of yobass

function for motion of yobass

functions and function for motion of yobass

functions and function points

functions and function points

functions

fu

This flexibility can be particularly useful in cases where you want your identifiers to be more descriptive or include specific characters, like special symbols, punctuation, or spaces. You can use extended identifiers to name something very precisely. For example, you can use a sentence as variable name. Extended identifiers can make your code more readable by allowing you to write names that are closer to natural language, or to conform to specific naming conventions that include special characters or symbols. You can use typical characters meant for common abbreviations like hashtags for 'number'. As in number of bits for instance. Just remember that these identifiers are enclosed in backslashes, and should be used carefully to maintain code readability and clarity. Note that, you escape the usual case-insensitivity with this feature and thus easily create three different identifiers with basically the same name as shown with the VHDL example at the bottom of the slide. Overall, extended identifiers provide additional flexibility for naming conventions. However, this kind of identifiers is rarely used in practice. Next, let's go over some important core VHDL constructs.

## **Extended Identifiers** HWMod **WS24** Extended identifier syntax: extended identifier ::= \graphic\_character{graphic\_character} \ Identifiers Special identifier enclosed by backslashes graphic\_character can contain: Upper-/lower-case letters (including language specific letters like ä, å, â) Digits Special characters (", #, &, ¾, etc.) Space characters Examples: \best'VAR'ev@r\ \# of bits\ \this const represents m in ~inch\ ■ VHDL, \VHDL\, \vhdl\ - three different identifiers

## −VHDL Basics └─Entity └─**Entity**

Sart by characterizing a hardware entity

Defines a modules interface

Bocclise name, input, and oxfpats

Encapeular inmail data

Backfore definition: no investeign of inner workings is needed

Example entity with no IVC:

Instity summaries

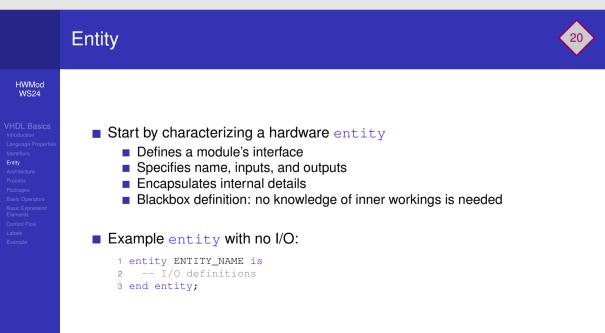

We start by covering entities. In VHDL, the concept of an entity is central to understanding how you describe hardware. An entity defines the external interface of a module. It tells us what the module is called and what its inputs and outputs are. Think of the entity as a blackbox that hides all the internal workings, showing only the essential connection points to the outside world. This abstraction is powerful because it allows you to focus on how components connect together without worrying about their internal details at this stage. Think of entities like a Java interface or an abstract Java object for which you define public input and output variables. In the example provided, you can see a simple entity that doesn't have any input or output. While this might seem trivial now, it forms the basis of all designs, no matter how complex they become.

## −VHDL Basics └─Architecture └─**Architecture**

Now that we've covered entities, let's move on to architectures. This is where the real work happens. Architecture describes the internal structure and behavior of an entity. In other words, it tells us how the entity's inputs are processed to produce the outputs. You can have multiple architectures for a single entity, each implementing different behaviors. Like multiple distinct Java objects for one interface. This will become more relevant later, when we start to cover hardware generation. For example, one architecture might be optimized for speed, while another is optimized for area or power consumption. This flexibility allows you to experiment with different design strategies without changing the entity's interface. In practice. architecture types are often named behaviorally, like 'behavioral' - or an abbreviation of that word - for a behavioral description, which describes how the entity works in a functional sense. The example shown here demonstrates an empty architecture with a generic name corresponding to a generic entity. Architectures start with the architecture keyword followed by the architecture name. Then you follow up naturally and specify "of" which entity this architecture is meant to be. Next is the declaration scope for constants and more. Elements in this scope are comparable to private class variables. After the begin keyword you would write the actual behavior of the specified entity. As already mentioned, in this introduction session we will write VHDL software programs rather than actual describing hardware. The goal is to make you familiar with basic VHDL constructs and syntax. We need a way to write sequential code in an architecture like we do in functions in Java or C. Thus, let's dive into a VHDL construct that supports exactly this.

|                                                                                                                                                                                                                                          | Architecture 23                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HWMod<br>WS24<br>HDL Basics<br>troducton<br>anguage Properties<br>dertifers<br>anguage Properties<br>dertifers<br>antity<br>urchitecture<br>rocess<br>hakages<br>lasic Operators<br>asic Expression<br>terments<br>control Flow<br>abels | <ul> <li>Describes the internal structure via architecture</li> <li>Defines how the entity's functionality is implemented <ul> <li>Knowledge of inner workings is needed</li> <li>How does the entity behave?</li> </ul> </li> <li>It is possible to define multiple architectures for a single entity <ul> <li>Typical names for architectures: beh/behavioral or struct/structural</li> </ul> </li> </ul> |

| abeis<br>ixample                                                                                                                                                                                                                         | <pre>Example: empty architecture     architecture ARCH_NAME of ENTITY_NAME is     constants, etc.     begin     description of inner workings of ENTITY_NAME     f end architecture;</pre>                                                                                                                                                                                                                  |

#### 7

afines how the entity's functionality is impler Knowledge of inner workings is needed How does the entity behave?

sposible to define multiple architectures for a single entity Typical names for architectures: betweetworks of a truct tample: empty architecture architecture architecture

#### └─VHDL Basics └─Process └─**Process**

Processes are an essential part of VHDL. They allow you to describe sequential operations within an architecture. While VHDL is primarily a parallel language, processes introduce the concept of time and ordering, allowing you to describe operations that depend on previous events. For now, we will focus only on this sequential operation paradigm. Within an architecture a process starts with the process keyword. After that follow declarations of constants and variables. We will show an example of that later. The begin keyword initiates the process body. Here are all the sequential statements of a process. Note that the last statement in the process is wait. This is important now such that you can write a program that can be executed once per run. As is usual with VHDL scopes the process ends with the end keyword and the kind of scope - in this case end process.

#### Process HWMod **WS24** Defines sequential execution within an architecture wait at the end signals process termination Example process: Process 1 architecture ARCH\_NAME of ENTITY\_NAME is 2 -- constants, etc. 3 begin 4 process -- constants, variables 5 6 begin 7 -- sequential statements 8 wait: 9 end process; 10 end architecture;

201

Defines sequential execution within an archit

wait at the end signals process termination

interface and make of entity make is

Example process:

#### −VHDL Basics └─Process └─**Variables & Constants**

Load within processes for temporary storage

Declared after process definition and before lines in

Loads the process definition and before lines in

Loads the process definition and before lines in

Declared attack with one observation

Orestarts: Read only and requires value on declaration

Example declarations of one constart and overvalues:

I antical key in antice in the process of the overvalues in

I antical key in the interpret of the overvalues in

I anticelar key in the interpret of the overvalues in

I anticelar key interpret of the overvalues in

I anticelar key interpret of the overvalues in

I anticelar key interpret of the overvalues in

21

Within processes, you often need to store intermediate values, and this is where variables and constants come into play. Variables in VHDL are local to the process they're defined in. Like variables in other programming languages they are updated immediately when you assign them a new value. Constants, on the other hand, are read-only values that must be assigned when they're declared. They are useful for values that shouldn't change, like mathematical constants or configuration parameters. The example here shows declarations of a constant followed by two integer variables. Constant and variable declarations are initiated with the constant and variable keywords, respectively. Follow up with the name, colon character and type name after which you can assign default values after colon equal. Note that the assignment for constants is mandatory. For variables, they are optional but recommended. For simplicity, we will only handle some built-in types in this lecture.

# Variables & Constants Image: Constant Strate St

## −VHDL Basics └─Packages └─**Packages**

Define reusable code modules via packages

Orstain common declarations: constants, types, functions, and

provides

Provides a contrain place to manage shared definitions

Provides a contrain place to manage shared definitions

Example packages default

()

45

Packages in VHDL are similar to libraries or modules in other programming languages. They allow you to define reusable code components like constants and in later lectures you will also find types, functions, and procedures here. Packages help to promote modularity by keeping common definitions and utilities in a single, manageable place. This is particularly useful in larger projects where multiple entities or architectures need to share the same data types or functions. We will cover types, functions and procedures in a later lecture. To declare a package, you start with the package keyword followed by the package name and the is keyword. Within the package, you can define various reusable components. After that, you end the package declaration with end package optionally followed by the package name. By organizing your code into packages, you can build up a library of reusable components that makes future design work easier and more efficient.

#### Packages 45 HWMod **WS24** Define reusable code modules via packages Contain common declarations: constants, types, functions, and procedures Promotes modularity and code reuse Packages Provides a central place to manage shared definitions Example package declaration: 1 package screenInfo is 2 -- constant declarations constant SCREEN\_WIDTH : integer := 720; 3 constant SCREEN HEIGHT : integer := 480; 4 5 end package;

## −VHDL Basics └─Packages └─**Using Packages**

Once a package is defined, you can use its contents in your design by importing it with the 'use' clause. This provides access to all the components that the package contains. To use a package, you start with the use keyword, followed by the library name, package name, and the all keyword to include everything. Alternatively, you can specify individual elements if you don't need the entire package. In the example, the line 'use work.screenInfo.all;' is used to import everything defined in the package 'screenInfo' from the previous slide located in the 'work' library. The 'work' library is the default library in VHDL where all your design units, like entities, architectures, and packages, are compiled by default. By specifying 'work', you are referring to the current working library for your project. You will get to know other important libraries in later lectures. The all keyword lets you import all types, constants, functions, and procedures that the package 'screenInfo' defines.

|                                                                                                                                                                                                                           | Using Packages                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HWMod<br>WS24<br>VHDL Basics<br>Introduction<br>Language Properties<br>Identifiers<br>Entity<br>Architecture<br>Process<br>Pacages<br>Basic Operators<br>Basic Spression<br>Elements<br>Control Flow<br>Labels<br>Example | <ul> <li>Import packages into your VHDL code with the use clause</li> <li>Provides access to types, constants, functions, and procedures defined in the package</li> <li>Use the following syntax: <ul> <li>use library_name.package_name.all;</li> <li>use library_name.package_name.element_name;</li> <li>Default library work: current project working library</li> </ul> </li> <li>Example of using a package:</li> </ul> |

|                                                                                                                                                                                                                           | <pre>1 make SCREEN_WIDTH, SCREEN_HEIGHT available to this file 2 use work.screenInfo.all; 3 4 entity declaration 5 6 entity architecture</pre>                                                                                                                                                                                                                                                                                 |

## −VHDL Basics └─Basic Operators └─**Basic Operators**

kasignment Operator: :orginal Operator: (kpop):-, /+, (, (, (, ))) kallorad Operatorial (kpop):-, /+, (, (, ))) etiminet Operatoria (kpop):-, (, ), (constantiation) kiterianto Operatoria (kpop):-, (, (operatoriation)) Miscolariona Operatoria (miscop): -, (exponentiation), size (absolute abue), next (logical regatoria)

150

Important: VHDL is a strongly typed language Types of both operands must match Result type on the left side must match operands on the right side of

Let's look at some basic operators in VHDL that you'll often use in your designs. We have the assignment operator, represented by the colon equals sign, used for assigning values to variables. There are logical operators like 'and' and 'or', which handle boolean values. Relational operators let you compare values and return a boolean result. Note that the equality operators differ from Java and C. For equality, VHDL uses a single equals sign, while inequality is represented by a slash followed by an equals sign. Arithmetic operators like plus and minus handle numeric operations The ampersand operator is also called concatenation operator. For now, it is only relevant for building strings. There are also operations for multiplication and divisions as well as modulo and remainder. The difference between mod and rem is that rem ensures the remainder has the same sign as the dividend. Lastly, there are helpful operators for exponentiation as well as unary operators to retrieve absolute values from integers and logical negotiations. Remember, VHDL is strongly typed, meaning operand types must match exactly, or you'll get an error. We'll see examples of these operators later. Next, we look at expressions.

## **Basic Operators**

#### HWMod WS24

VHDL Basics Introduction Language Properties Identifiers Entity Process Prackapes Basic Depression Elements Control Flow Labels Example

- Assignment Operator: :=

- Logical Operators (*logop*): and, or, nand, nor, xor, xnor

- Relational Operators (*relop*): =, /=, <, <=, >, >=

- Used for comparing values, returns a boolean result

- Arithmetic Operators (*addop*): +, -, & (concatenation)

- Multiplication Operators (mulop): \*, /, mod, rem

- Miscellaneous Operators (*miscop*): \*\* (exponentiation), abs (absolute value), not (logical negation)

- Important: VHDL is a strongly typed language

- Types of both operands must match

- Result type on the left side must match operands on the right side of assignments

## └─VHDL Basics └─Basic Expression Elements └─**Basic Expression Elements**

prim ::- lit | const 5, '', trum, chi/freq

factor ::- (prim) | (abs prim) | (not prim) abs -2, cot true, 5 +: 2

trum ::- factor (malor factor) 5 - 2, 10 / 2, 7 end 3

140

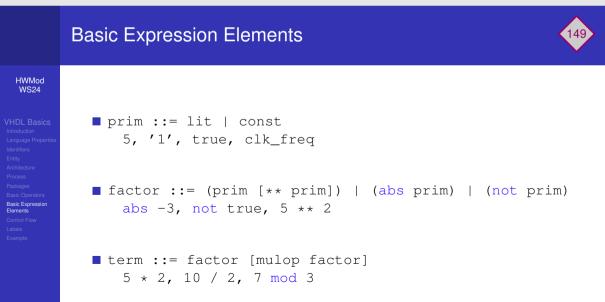

Let's start by breaking down the fundamental elements of VHDL expressions. The most basic building blocks are primitives, like literals or constants. For example, the number five, the character '1', or a predefined constant like true or a variable name. Factors are slightly more complex; they can include exponentiation, absolute values, or logical negation. A term combines factors using multiplication or division operators. Understanding these basic elements is crucial, as they form the foundation for more complex expressions.

#### 13

## └─VHDL Basics └─Basic Expression Elements └─**Combining Elements into Expressions**

$\label{eq:approximation} \begin{array}{l} \textbf{s} = spec ::: (r) < 1 \text{ term } [addup term] \\ 3 + 2_r - 1 + 7_r \text{ remain } - 5 \end{array}$

40

Now let's look at how we build more advanced expressions using the basic elements from the previous slide. A simple expression, can be formed by combining terms with addition or subtraction. Relations allow us to compare two expressions, using relational operators like greater than or equal to. At the highest level, an expression can be a relation or a combination of multiple relations. By mastering these building blocks, you can construct most logical expressions you need in VHDL. Note that the operations and expression definitions are also available on the VHDL cheat sheet which you can find on this course's TUWEL page.

# Combining Elements into Expressions

#### HWMod WS24

VTIDE DASIGN Introduction Language Propertie Identifiers Entity Architecture Process Packages Basic Coperators Basic Expression Elements Control Flow Labels Example sexpr ::= [+/-] term [addop term]

3 + 2, -1 + 7, result - 5

expr ::= relation [logop relation]

(a = b) or (c > d)

## −VHDL Basics └─Basic Expression Elements └─**Basic Sequential Statements**

Hand's support

Analysis the value of an expression to a validate (thrut)

Analysis the value of an expression to a validate (thrut)

Analysis the value of the

140

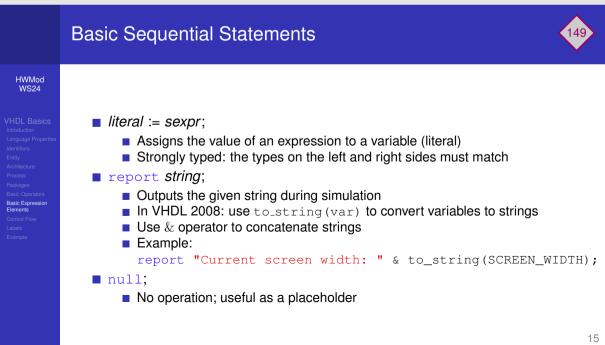

Let's review some basic sequential statements used in VHDL. Again, the assignment operator allows us to assign a value to a variable. Assignments require a simple expression on the right side. Remember, VHDL is strongly typed, so both sides of the assignment must have compatible types. The report statement is used to output messages during simulation, which can be helpful for debugging. You can convert variables to strings using the "to-string" function introduced in VHDL 2008 and concatenate multiple strings using the ampersand operator. Finally, the null statement represents a no-operation, useful when a statement is required syntactically, but no action is needed. Before writing our first program let's also talk about control flow operations.

## -VHDL Basics Control Flow **Control Flow: Branching**

form Ada.

Control flow is crucial in programming as it allows your code to make decisions based on certain conditions. Let's start with the if-else statement. The if-else statement in VHDL works similarly to other programming languages. It checks a condition represented by an expression, and executes a block of sequential statements if this condition is true. If the condition is false, the program can optionally check additional conditions using 'else-if' branches, or execute a default block of statements using the else branch. Note that "else-if" branches are introduced with somewhat uncommon elsif keyword, a guirk inherited Next, we have the case statement, which is used when you want to select one of many possible actions based on the value of an expression. The case statement compares the expression against a series of choices. When a match is found, the corresponding block of sequential statements is executed. A default action can be specified, in case not all possible values the expression can evaluate to are covered. A choice statement consists of a simple expression or the others keyword. 'Others' is essentially like the 'else' keyword in if statements or 'default' in Java's and C's switch-case. The case statement is particularly useful when dealing with enumerated types or situations where multiple distinct conditions need to be handled differently. There is no fall through like in Java or C in VHDL so no 'break'-like keyword is required. A choice only executes the sequential statements below the choices. A valid case statement has to cover all possible choices

from the expression. This is where the 'others' keyword as default branch comes in handy. The case statement will become very useful in later lectures. Especially when enumerated types are handled.

|                                                                                                                                                                                                    | Control Flow: Branching                                                                                                                                                                              | 193<br>193                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HWMod<br>WS24<br>VHDL Basics<br>Introduction<br>Language Properties<br>Identifiers<br>Packages<br>Packages<br>Basic Operators<br>Basic Expression<br>Elements<br>Control Flow<br>Labels<br>Example | <pre>if/else:     if expr then         {sequential statement}         [{elsif expr then             {sequential statement}}]         [else             {sequential statement}]         end if;</pre> | <ul> <li>select:<br/>case expr is<br/>{when choice [{ choice}] =&gt;<br/>{sequential statement}}<br/>end case;</li> <li>choice ::= sexpr   others</li> <li>All possible choices must be<br/>covered</li> </ul> |

#### 16

193

aice [{]

(sequential sta

choice :-- cover l ---

unotial statems

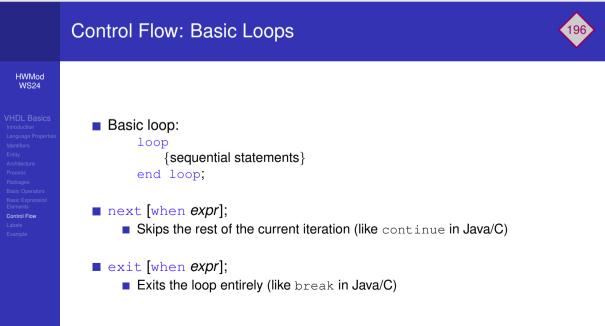

## └─VHDL Basics └─Control Flow └─**Control Flow: Basic Loops**

Basic loop: interpretation (assumed)) estimation (association) estimation (association) Basics frame off): Basics frame off): Each to loop official (association) (Basics)(association) estimation (Basics)): Each to loop official (Basics) (association) (association) Each to loop official (Basics) (association) (association) (basics)): Each to loop official (Basics) (association) (as 195

Let's begin by looking at basic loops in VHDL. A basic loop is created using the loop keyword, and it will continue indefinitely unless you use a control statement to break out of it. This is similar to an infinite loop in other programming languages. To control the flow within the loop, you can use the next statement, which skips the rest of the current iteration and moves to the next one, similar to the continue statement in Java or C. The exit statement, is used to exit the loop entirely, much like the "break" statement in other languages. Both next and exit can be used with an optional when clause to conditionally control the loop's behavior.

## └─VHDL Basics └─Control Flow └─**Control Flow: Typed Loops**

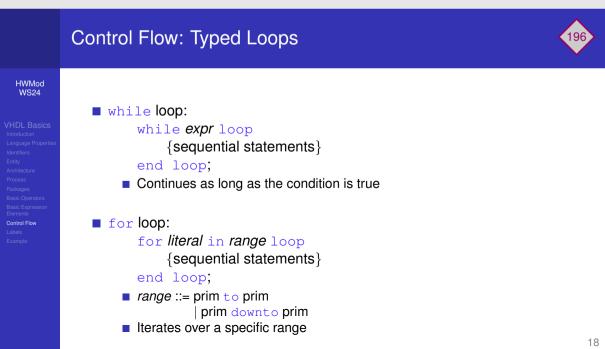

Now, let's look at typed loops in VHDL. The while loop continues execution as long as the condition specified in the while expression is true. This is similar to while loops in other programming languages, where the loop checks the condition before each iteration. On the other hand, the for loop is used to iterate over a specific range of values, defined by either the to or downto keywords. With the for loop, you specify a loop parameter, which takes on each value in the range, one at a time. Note that the VHDL standard defines this loop parameter to be a constant inside the loop. Thus, when executing the sequential statements of the loop's body, the loop parameter cannot be modified. Both loops allow you to control repetitive actions in your VHDL code, but they are suited for different situations depending on whether you know the number of iterations in advance or need to rely on a condition.

195

while loop: while expr loop {sequential statements}

tinues as inon as the condition is true

## --VHDL Basics └--Labels └--**Miscellaneous: Block Identifiers & Labels**

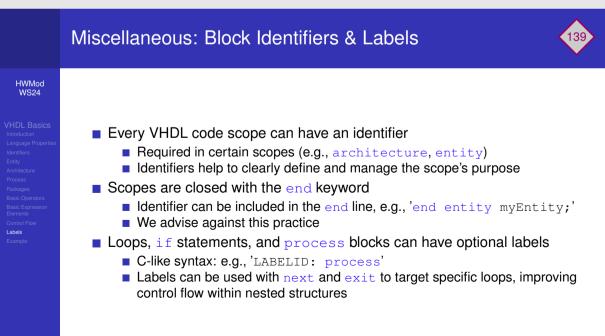

Every VHDL code scope can have an identifier

Headed in code in the state of the scope o

130

Lastly, before showing a complete VHDL code example let's quickly talk about labels. In VHDL, every scope of code, such as an architecture or entity, can have an identifier. While not always required, identifiers help manage and clearly define the scope, making the code more readable and maintainable. Loops, if-statements, and process blocks can also have optional labels. Scopes are closed with the end keyword, and it's possible to include the identifier in the end statement as well. However, we discourage you from do this, as it introduces unnecessary work when something needs to be renamed and modern IDEs or code editors visualize this scopes anyway. Using labels can greatly improve the readability of your VHDL code, especially in complex or nested structures. It is possible to target specific nested loop hierarchies with the control flow statements 'next' and 'exit'. Overall, thoughtful use of identifiers and labels enhances code clarity and maintainability. Additionally, keep in mind that labeling structures can help you find and debug problems in simulations later.

## └─VHDL Basics └─Example └─**Example Process: Fibonacci**

main process main process explosite process, provides, temp r indeper in 0; begin explosite process process in process in process for i in 5 to 9752\_GODE imp provides in temp; provides in temp; provides interface process i correct; provides i corr

Now lets finally put everything together and look at a bigger more comprehensive example. You are probably familiar with the Fibonacci sequence. The Fibonacci sequence is a series of numbers where each number is the sum of the two preceding ones, starting from 0 and 1. In this slide you can see the implementation of this sequence in a process. Let's start from the top. We call the process 'main' by labeling it. Then we define the constant UPPER\_BOUND which limits the number of calculated Fibonacci numbers. Three variables are required in this implementation to calculate the sequence. We start the process by assigning 0 to 'previous' and 1 to 'current'. Then we start a loop declare a loop variable i and let the loop repeat from the range 0 to UPPER\_BOUND. The loop body contains statements such that we calculate the next Fibonacci number by summing up the two previous ones. After which we print the current Fibonacci number via the 'report' command by concatenating a few constant string with two variables with the help of the to\_string function. We end the loop, and finally, before we terminate the process we add the -for now- required 'wait' statement. We will now show you how you can easily test and play around with this code.

## Example Process: Fibonacci

```

HWMod

WS24

```

```

VHDL Basics

Introduction

Language Properties

identifiers

Entity

Architecture

Process

Packages

Basic Operators

Basic Expression

Elements

Control Flow

Labels

Example

```

```

1 main: process

constant UPPER_BOUND : integer := 20;

2

variable current, previous, temp : integer := 0;

3

4 begin

previous := 0;

5

6

current := 1;

for i in 0 to UPPER BOUND loop

7

temp := current;

8

current := previous + current;

9

previous := temp;

10

report "Fibonacci(" & to_string(i) & ") = "

11

& to_string(current);

12

end loop;

wait;

14

15 end process;

```

## └─VHDL Basics └─Example └─**Testing: EDA Playground Overview**

Web-bases platform for simularly and sharing HCL code

Instruct / or weblicitystream curve.

Seport multiple languages:

VFCL, Wind, Systembridg, and more

Fatters:

VFCL, Wind, Systembridg, and more

Fatters:

Noticetable (e.g., CHCL, Modellin (CuestaSim)

Codecades on the Bowers

Noticetable (e.g., CHCL, Modellin (CuestaSim)

Codecades on the Bowers

Noticetable (e.g., CHCL, Modellin (CuestaSim)

Setting and Statugers and ucces separate

Elandes

Elandes (e.g., CHCL, Modellin (CuestaSim)

Elandes

Elandes

Elandes

Codecades on the Bowers

Elandes

Elandes

For this purpose we will use the EDA Playground. This is a Web-based platform for testing HDL code in general. It has a lot of features but for now just see it as a tool to execute VHDL code.

# Testing: EDA Playground Overview

#### HWMod WS24

#### VHDL Basics Introduction Language Properties Identifiers Entity Architecture Process Basic Operators Basic Operators Basic Spression Elements Control Flow Labels Fxame

- Web-based platform for simulating and sharing HDL code

- https://www.edaplayground.com/

- Supports multiple languages:

- VHDL, Verilog, SystemVerilog, and more

- Features:

- Access to various simulators (e.g., GHDL, ModelSim (QuestaSim))

- Collaborative coding with sharing links

- No installation needed, runs in the browser

- Ideal for:

- Learning and practicing HDL coding

- Testing and debugging small code snippets

- Demonstrating concepts in a classroom setting

## └─VHDL Basics └─Example └─EDA Playground Settings

| Innerin in 🔬 DOULOS<br>• Languages & Libraries<br>Testerch - Geolge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ul> <li>Set Testbench + Design langua<br/>to VHDL</li> <li>Set Libraries to OSVVM</li> </ul> |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| Uberries Ø                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <ul> <li>Open Source VHDL Verificat<br/>Methodology</li> </ul>                                |

| CVL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ul> <li>Specify "Top entity"</li> </ul>                                                      |

| South State | "main" entity: myEntity in f                                                                  |

| Top entity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | example (see testbench.vhd                                                                    |

| inyGritty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | next slide)                                                                                   |

| Enable Vant o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Select GHDL 3.0.0 as Simula                                                                   |

| <ul> <li>Tools &amp; Simulators e</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Open Source VHDL Simulato                                                                     |

| 0404.3.00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                               |

First, focus on the left side of the website and check out the settings. Start from the top. To run the Fibonacci example start by setting the 'Testbench + Design' language to VHDL. Then select OSVVM under 'Libraries'. Specify the so called 'Top entity'. This is generally the highest order entity in your design. We will only use one entity called 'myEntity'. So specify 'myEntity' as top entity. Lastly, select GHDL 3-O-O under Tools and Simulators.

# **EDA Playground Settings**

| HWMod |  |

|-------|--|

| WS24  |  |

| VHDL Basics |

|-------------|

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

|             |

| Example     |

|             |

|             |

|             |

| EDA                                           |  |  |  |

|-----------------------------------------------|--|--|--|

| Brought to you by ADOULOS                     |  |  |  |

| <ul> <li>Languages &amp; Libraries</li> </ul> |  |  |  |

| Testbench + Design                            |  |  |  |

lauraun

$\sim$

$\sim$

VHDL

#### Libraries 🕜

OVL OSVVM UVVM

#### Top entity

myEntity

Enable VUnit 🚯

Tools & Simulators Ø

GHDL 3.0.0

- Set Testbench + Design language to VHDL

- Set Libraries to OSVVM

- Open Source VHDL Verification Methodology

- Specify "Top entity"

- "main" entity: myEntity in this example (see testbench.vhd on next slide)

- Select GHDL 3.0.0 as Simulator

- Open Source VHDL Simulator

## └─VHDL Basics └─Example └─EDA Playground Code

Now it's time to code! Move your attention to the right and check out the two input fields or editors. Put your code into the default testbench.vhd file in the left editor. This includes your top entity declarations and architecture for your entity. Put your process inside the architecture. GHDL requires a non-empty design file. So just put in some random empty design on the right-most editor.

# EDA Playground Code

testbench.vhd

#### HWMod WS24

VHDL Basics Introduction Language Properties Identifiers Entity Architecture Process Packages Basic Expression Elements Control Flow Labels **Example**

| 1      | entity myEntity is                                          |                                      |

|--------|-------------------------------------------------------------|--------------------------------------|

|        | end entity;                                                 |                                      |

| 3      | end entity;                                                 | 4                                    |

|        | architecture heb of myEntity is                             | 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 |

| 5      | architecture beh of myEntity is                             | 4                                    |

| 2      | begin                                                       | 5                                    |

| 6<br>7 |                                                             | 6                                    |

|        | main: process                                               | 1                                    |

| 8      | constant UPPER_BOUND : integer := 20;                       | 8                                    |

| 9      | <pre>variable current, previous, temp : integer := 0;</pre> |                                      |

| 10     | begin                                                       | 10                                   |

| 11     | previous := 0;                                              | 11                                   |

| 12     | current := 1;                                               | 12                                   |

| 13     | for i in 0 to UPPER_BOUND loop                              | 13                                   |

| 14     | temp := current;                                            | 14                                   |

| 15     | current := previous + current;                              | 15                                   |

| 16     | previous := temp;                                           | 16                                   |

| 17     | report "Fibonacci(" & to_string(i) & ") = "                 | 17                                   |

| 18     | & to string(current);                                       | 18                                   |

| 19     | end loop;                                                   | 19                                   |

| 20     | wait;                                                       | 20                                   |

| 21     | end process;                                                | 21                                   |

| 22     | end architecture;                                           | 22                                   |

|        |                                                             |                                      |

Put your code (entity + architecture) into the testbench file on the left

entity design is

end entity;

GHDL requires a non-empty design file on the right

## └─VHDL Basics └─Example └─EDA Playground Output

Now you can click 'run' to execute your VHDL code. If done correctly it should compile and print output on the bottom part of the webpage. In our case it printed our string as specified via the report command. Note that VHDL simulators usually print out a lot of additional information if printing via 'report'. In GHDL's case it's the filename and position of the report command in addition to the simulation timestamp. You can check the code and see that the report statement is indeed in line 16 and starts at character 11. The timestamp will become more important later when we dive into advanced simulations. And that's it for this session! You can play around with the provided example and get a better feeling of the basic VHDL syntax set as shown in this lecture. For this particular example keep in mind that the integer type is only 32-bit wide. So do not set the UPPER\_BOUND constant arbitrarily big.

tbench.vhd

# **EDA Playground Output**

< Share

#### HWMod WS24

Example

|  | [2024-08-14 14:15:08 UTC] ghdl -            | ist    | d=08 design. | vhd   | testbe |

|--|---------------------------------------------|--------|--------------|-------|--------|

|  | analyze testbench.vhd                       |        |              |       |        |

|  | elaborate myentity                          |        |              |       |        |

|  | testbench.vhd:16:11:@0ms:(report            | note): | Fibonacci(0  | ) = 1 | L      |

|  | testbench.vhd:16:11:@0ms:(report            | note): | Fibonacci(1  | ) = 2 | 2      |

|  | testbench.vhd:16:11:@0ms:(report            | note): | Fibonacci(2  | ) = 3 | 3      |

|  | testbench.vhd:16:11:@0ms:(report            | note): | Fibonacci(3  | ) = 5 | 5      |

|  | testbench.vhd:16:11:@0ms:(report            | note): | Fibonacci(4  | ) = 8 | 3      |

|  | testbench.vhd:16:11:@0ms:(report            | note): | Fibonacci(5  | ) = 1 | 13     |

|  | testbench.vhd:16:11:@0ms:(report            | note): | Fibonacci(6  | ) = 2 | 21     |

|  | testbench.vhd:16:11:@0ms:(report            | note): | Fibonacci(7  | ) = 3 | 34     |

|  | testbench.vhd:16:11:@0ms:(report            | note): | Fibonacci(8  | ) = 5 | 55     |

|  | testbench.vhd:16:11:@0ms:(report            | note): | Fibonacci(9  | ) = 8 | 39     |

|  | testbench.vhd:16:11:@0ms:(report            | note): | Fibonacci(1  | 0) =  | 144    |

|  | testbench.vhd:16:11:@0ms:(report            | note): | Fibonacci(1  | 1) =  | 233    |

|  | testbench.vhd:16:11:@0ms:(report            | note): | Fibonacci(1  | 2) =  | 377    |

|  | testbench.vhd:16:11:@0ms:(report            | note): | Fibonacci(1  | 3) =  | 610    |

|  | <pre>testbench.vhd:16:11:@0ms:(report</pre> | note): | Fibonacci(1  | 4) =  | 987    |

|  | <pre>testbench.vhd:16:11:@0ms:(report</pre> | note): | Fibonacci(1  | 5) =  | 1597   |

|  | testbench.vhd:16:11:@0ms:(report            | note): | Fibonacci(1  | 6) =  | 2584   |

|  | <pre>testbench.vhd:16:11:@0ms:(report</pre> | note): | Fibonacci(1  | 7) =  | 4181   |

|  | <pre>testbench.vhd:16:11:@0ms:(report</pre> | note): | Fibonacci(1  | 8) =  | 6765   |

|  | <pre>testbench.vhd:16:11:@0ms:(report</pre> | note): | Fibonacci(1  | 9) =  | 10946  |

|  | testbench.vhd:16:11:@0ms:(report            | note): | Fibonacci(2  | 0) =  | 17711  |

|  | Deere                                       |        |              |       |        |

- Outputs Fibonacci sequence

- Caution if you try higher UPPER\_BOUND: integer is 32-bit wide

Thank you for listening! We recommend you to immediately take the self-check test in TUWEL, to see if you understood the material presented in this lecture.

#### /HDL BASICS Introduction Language Propertie Identifiers Entity Architecture Process Packages Basic Operators Basic Expression Elements

Labels

Example

# Lecture Complete!

Modified: 2025-03-30, 16:53 (e9b236f)