# Hardware Modeling [VU] (191.011) – WS25 –

## Synchronizers and Debouncers

Florian Huemer & Sebastian Wiedemann & Dylan Baumann

WS 2025/26

# Recall: MTBU Estimation

HWMod

WS25

Sync. & Deb.

Recap

Synchronizers

Debouncing

- We can get a statistical estimate of the MTBU

$$MTBU = \frac{1}{\lambda_{in} \cdot f_{clk} \cdot T_W} \cdot e^{\frac{t_{res}}{\tau_C}}$$

- Exponential dependence of MTBU on time to resolve  $t_{res}$

- Increasing  $t_{res}$  is a mechanism to increase the MTBU

- However: MTBU can never become infinite!

- Harnessed by *synchronizers*

- Trade-off performance for a higher MTBU

# Waiting Synchronizers

HWMod

WS25

Sync. & Deb.

Recap

Synchronizers

VHDL

Take Aways

Debouncing

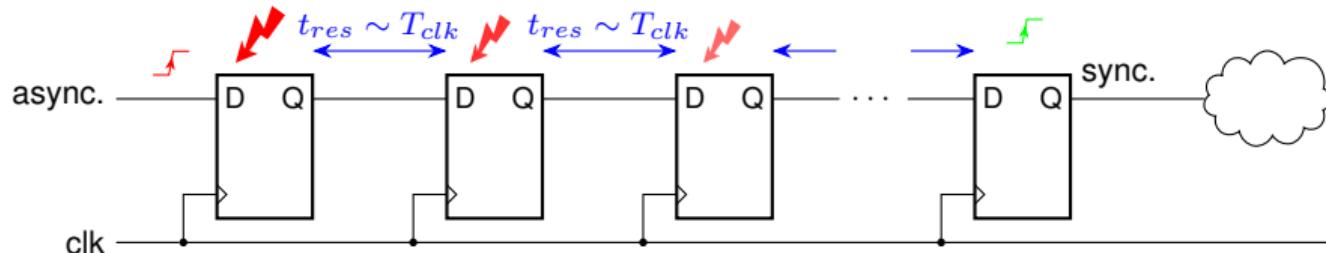

- Chain of flip-flops

- Pass metastable output to next flip-flop in chain

- No comb. logic between flip-flops  $\Rightarrow$  majority of clock period for resolution

- Asynchronous input is “synchronized” to the clock

- Overall resolution time is the sum of the individual ones

- $\Rightarrow$  Exponential increase in MTBU **per** flip-flop

- In practice often two flip-flops, three to be on the safe side

- Trade-off between latency and MTBU

# VHDL Implementation

HWMod

WS25

Sync. & Deb.

Recap

Synchronizers

VHDL

Take Aways

Debouncing

```

1 library ieee;

2 use ieee.std_logic_1164.all;

3

4 entity synchronizer is

5   generic (

6     STAGES : natural;

7     RES_VAL : std_ulogic

8   );

9   port (

10     clk    : in std_ulogic;

11     res_n : in std_ulogic;

12     async : in std_ulogic;

13     sync  : out std_ulogic

14   );

15 end entity;

16

16 architecture arch of synchronizer is

17   signal ffs: std_ulogic_vector(0 to STAGES);

18 begin

19   process (clk, res_n) begin

20     if res_n = '0' then

21       ffs <= (others => RES_VAL);

22     elsif rising_edge(clk) then

23       ffs(0) <= async;

24       for i in 1 to STAGES loop

25         ffs(i) <= ffs(i-1);

26       end loop;

27     end if;

28   end process;

29   sync <= ffs(STAGES);

30 end architecture;

```

# Important Aspects

HWMod

WS25

Sync. & Deb.

Recap

Synchronizers

VHDL

Take Aways

Debouncing

- MTBU can be made *arbitrarily* large by appropriate synchronizer

- A synchronizer does **not** prevent metastability!

- A single flip-flop alone is not a synchronizer

- The MTBU is a statistical quantity

- No guarantee for upset-freedom at any time

# Bouncing Inputs

HWMod

WS25

Sync. & Deb.

Recap

Synchronizers

Debouncing

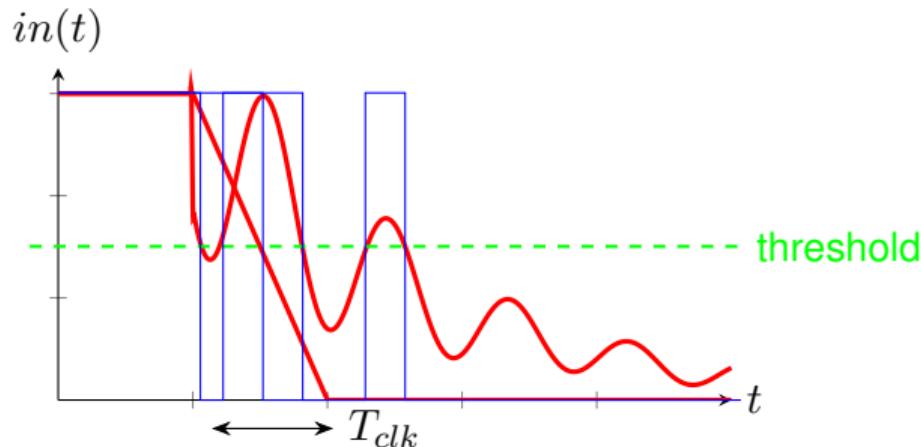

- Asynchronous inputs are not the only problem at interfaces

- Some mechanical contacts may “bounce” due to their construction

- For example: Mechanical buttons, switches

- Instead of clean transition damped oscillation

- Depending on clock frequency, takes multiple (hundred) clock cycles

- May upset input FFs or leads to unwanted transitions

# Counter Measures

HWMod

WS25

Sync. & Deb.

Recap

Synchronizers

Debouncing

- Simply filter-out sequence of input transitions that is “too fast”

- Analog (low pass) filtering

- Digital filtering to check if output stabilizes

- Use timer to wait (FSM)

- Alternatives exist

- Software-based debouncing

# Debouncer Implementation

HWMod

WS25

Sync. & Deb.

Recap

Synchronizers

Debouncing

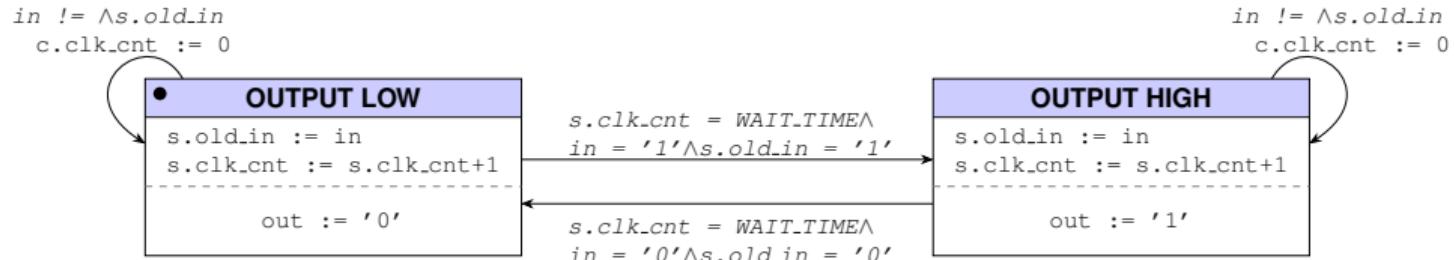

## ■ Digital debouncing FSM

- Debouncer either outputs zero or high

- If the input changes, reset counter to count time since transition

- When input change is stable, change output

# Lecture Complete!