In this lecture we will deepen our knowledge and skills regarding practical hardware design using VHDL and structural modelling.

#### Struct. Mod. Introduction Instances Components Architecture Selection

#### Hardware Modeling [VU] (191.011) - WS24 -

Structural Modeling

Florian Huemer & Sebastian Wiedemann & Dylan Baumann

#### WS 2024/25

Modified: 2025-03-12, 16:33 (21636bb)

## -Structural Modeling

|                                  | Behavior                                                         | Structure | Geometry             |

|----------------------------------|------------------------------------------------------------------|-----------|----------------------|

| System Level                     | inpuni Keykseni<br>Gulgun Display<br>Austrian                    | 222       |                      |

| Algorithmic<br>Level             | ahija input<br>Kasil<br>(Antilleg'<br>Galakes Kara<br>Dagky Janr |           | 10 100<br>10.04 1000 |

| Register Transfer<br>Level (RTL) | NACT Own<br>Ave for 1<br>dear<br>Ave A<br>ave 2                  | である       | ΦΦΦ                  |

| Logic Level                      | 0 = NOT E<br>C = (0-28 8),480 A                                  | 40-0      | 動す                   |

| Circuit Level                    | *-*-*                                                            | ईदद^ई     | <b>聖</b> 臣           |

A fundamental aspect of any hardware description language is its support for hierarchical design, enabling the creation of complex circuits by assembling simpler building blocks into larger systems. To understand the significance of this, imagine an object-oriented programming language that prohibits objects from containing other objects. Obviously, such a language would be severely limited in its utility. This design approach corresponds to the logic and register-transfer levels on the structural axis of the Y-Diagram, which is why it is called "structural modeling".

#### Introduction

HWMod WS24

Struct. Mod. Introduction Instances Components Architecture Selection

|                                  | Behavior                                                              | Structure                                                                                                              | Geometry                 |

|----------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------|

| System Level                     | Inputs : Keyboard<br>Output: Display<br>Funktion:                     |                                                                                                                        | IN<br>OUT                |

| Algorithmic<br>Level             | while input<br>Read<br>"Schilling"<br>Calulate Euro<br>Display "Euro" | Memory<br>16 8 Interface<br>μP IO-Ctrl P5/2<br>Interface                                                               | μΡ PS/2<br>10-Ctrl R5232 |

| Register Transfer<br>Level (RTL) | if A=`1` then<br>B:= B+1<br>else<br>B:= B<br>end if                   | RAM Register                                                                                                           |                          |

| Logic Level                      | D = NOT E<br>C = (D OR B) AND A                                       | B<br>B<br>A                                                                                                            |                          |

| Circuit Level                    | $\frac{dU}{dt} = R\frac{dI}{dt} + \frac{1}{C} + L\frac{d^2I}{dt^2}$   | $\begin{array}{c} + \zeta & + \zeta & + \zeta \\ - 4 \zeta & - 4 \zeta & - 4 \zeta \\ + \zeta & - 4 \zeta \end{array}$ | ₹Ē                       |

#### −Structural Modeling └─Introduction └─Introduction (cont'd)

Create complex modules by combining and interconnecting (simpler) sith-modules

Hence, structural modeling can be defined as the process of combining and interconnecting modules to create more complex modules in a hierarchical fashion. Including an entity as a sub-module in another design unit in VHDL is referred to as instantiation – the included sub-module being the instance. At this point, let us also define some other commonly used terms in hardware design and testing related to instantiations that will be used throughout this course.

#### Introduction (cont'd)

#### HWMod WS24

Struct. Mod. Introduction Instances Components Architecture

#### Structual Modeling

Create complex modules by combining and interconnecting (simpler) sub-modules.

#### −Structural Modeling └─Introduction └─Introduction (cont'd)

Smithed Modeling Dreate complex modules by combining and interconnecting (simpler) ub-modules. Sop Level Design Entity The design unit (entity) that sits on highest layer of a hierarchical hardware design.

The top-level entity or top-level design refers to the highest or outermost module in a hierarchical design. It is the main component that integrates all the lower-level modules and subcomponents. This top-level entity serves as the entry point for the design and defines the inputs and outputs that connect the circuit to external systems.

#### Introduction (cont'd)

#### HWMod WS24

Struct. Mod. Introduction Instances Components Architecture

#### Structual Modeling

Create complex modules by combining and interconnecting (simpler) sub-modules.

#### Top-Level Design/Entity

The design unit (entity) that sits on highest layer of a hierarchical hardware design.

#### −Structural Modeling └─Introduction └─Introduction (cont'd)

Another term that you will also hear quite often is Unit-Under-Test or UUT. It refers to the entity that is instantiated in a testbench to validate its functionality.

#### Introduction (cont'd)

#### HWMod WS24

Struct. Mod. Introduction Instances Components Architecture

#### Structual Modeling

Create complex modules by combining and interconnecting (simpler) sub-modules.

#### Top-Level Design/Entity

The design unit (entity) that sits on highest layer of a hierarchical hardware design.

#### Unit Under Test (UUT)

The module instantiated in a testbench and whose behavior is verified.

Laboration and an angle of the second second

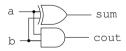

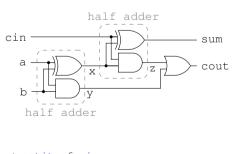

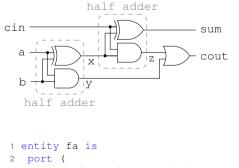

Before we go into details on the formal syntax specification of instantiations in VHDL, let us first look at a simple code example. Consider the half adder circuit shown on this slide, which is used to calculate the sum and carry of two single-bit inputs and consists of a single "XOR" and "AND"-gate. We want to construct this circuit out of the two entities shown on the slide. These two modules should already look quite familiar to you, as they simply use one concurrent signal assignment to implement their desired behaviors. Also notice that we used the std\_ulogic datatype for its inputs and outputs.

#### Creating Instances – Example: Half Adder HWMod **WS24** sum cout Instances 1 entity xor\_gate is 1 entity and\_gate is 2 port ( 2 port ( a, b : in std\_ulogic; a, b : in std\_ulogic; 3 x : out std\_ulogic x : out std\_ulogic 4 4 ); 5 ); 5 6 end entity; 6 end entity; 7 7 8 architecture arch of xor\_gate is 8 architecture arch of and\_gate is 9 begin 9 begin 10 x <= a xor b; 10 $x \leq a$ and b; 11 end architecture; 11 end architecture;

International distance of the second distance of the se

Here, we see an implementation of the half adder circuit using instances of the entities shown on the previous slides.

#### Creating Instances – Example: Half Adder

#### HWMod WS24

```

1 entity ha is

2 port (

3

a, b : in std_ulogic;

sum, cout : out std_ulogic

4

5

);

6 end entity;

8 architecture arch of ha is

9 begin

10 and_gate_inst : entity work.and_gate

11 port map (a, b, cout);

12

13 xor_gate_inst : entity work.xor_gate

14 port map (a, b, sum);

15 end architecture;

```

- Instances → statement part

- Two instantiation statements

- Positional association

- Inputs must be readable, outputs writable

Its entity declaration lists the inputs a and b as well as the outputs sum and cout.

#### Creating Instances – Example: Half Adder

HWMod WS24

Struct. Mod. Introduction Instances Port Map Unused Ports Generic Map Components Architecture Selection

```

2 port (

3

a, b : in std_ulogic;

sum, cout : out std_ulogic

4

5

);

6 end entity;

8 architecture arch of ha is

9 begin

10 and_gate_inst : entity work.and_gate

port map (a, b, cout);

11

12

13 xor_gate_inst : entity work.xor_gate

14 port map (a, b, sum);

15 end architecture;

```

1 entity ha is

- Instances → statement part

- Two instantiation statements

- Positional association

- Inputs must be readable, outputs writable

As already discussed in a previous lecture, in VHDL instances are created in the statement part of architectures.

#### Creating Instances – Example: Half Adder

#### HWMod WS24

```

1 entity ha is

2 port (

3

a, b : in std_ulogic;

sum, cout : out std_ulogic

4

5

);

6 end entity;

8 architecture arch of ha is

9 begin

10 and_gate_inst : entity work.and_gate

port map (a, b, cout);

11

12

xor_gate_inst : entity work.xor_gate

13

14 port map (a, b, sum);

15 end architecture;

```

- Instances → statement part

- Two instantiation statements

- Positional association

- Inputs must be readable, outputs writable

To do so, one has to select a name for the instance followed by a colon and the name of the object that should be instantiated.

#### Creating Instances – Example: Half Adder

#### HWMod WS24

```

1 entity ha is

2 port (

3

a, b : in std_ulogic;

sum, cout : out std_ulogic

4

5

);

6 end entity;

8 architecture arch of ha is

9 begin

10 and_gate_inst : entity work.and_gate

port map (a, b, cout);

11

12

13 xor_gate_inst : entity work.xor_gate

14 port map (a, b, sum);

15 end architecture;

```

- $\blacksquare Instances \rightarrow statement part$

- Two instantiation statements

- Positional association

- Inputs must be readable, outputs writable

with μ = 1 (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1) (1 + 1

Then the port map statement is used to connect the interface signals of the instance to local signals available in the architecture.

#### Creating Instances – Example: Half Adder

#### HWMod WS24

```

1 entity ha is

2 port (

3

a, b : in std_ulogic;

sum, cout : out std_ulogic

4

5

);

6 end entity;

8 architecture arch of ha is

9 begin

10 and_gate_inst : entity work.and_gate

port map (a, b, cout);

11

12

13 xor_gate_inst : entity work.xor_gate

14 port map (a, b, sum);

15 end architecture;

```

- $\blacksquare Instances \rightarrow statement part$

- Two instantiation statements

- Positional association

- Inputs must be readable, outputs writable

Implementation

Implementation</l

For our half adder example circuit we create two instances – one of each of the basic gates shown on the previous slide. The local signals in the half adder architecture are connected to the interface signals of the entities using positional association. This works exactly like with aggregate expressions – already introduced in a previous lecture to initialize records. The signals are simply connected in the sequence of how they appear in the entity declaration of the instantiated entities. For our example this means that the local signal a is connected to the ports named a of the instances, just as b is connected to b inputs. The output x of the and gate is connected to cout, while the XOR's output is connected to the sum signal. Of course it must be ensured that signals that are connected to outputs of an instance are actually writable in the instantiation architecture. Similarly, input signals must be readable. It would, for example, lead to a compilation error if the x output of one of the gates would be connected to the a input of the half adder.

#### Creating Instances – Example: Half Adder

HWMod WS24

```

1 entity ha is

port (

2

3

a, b : in std_ulogic;

sum, cout : out std_ulogic

4

5

);

6 end entity;

8 architecture arch of ha is

9 begin

and_gate_inst : entity work.and_gate

10

port map (a, b, cout);

11

12

xor_gate_inst : entity work.xor_gate

13

port map (a, b, sum);

14

15 end architecture;

```

- Instances → statement part

- Two instantiation statements

- Positional association

- Inputs must be readable, outputs writable

#### └─Structural Modeling └─Instances └─**Port Map**

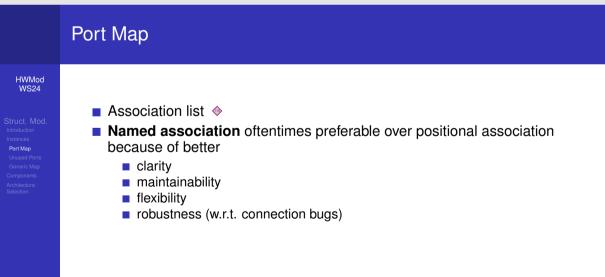

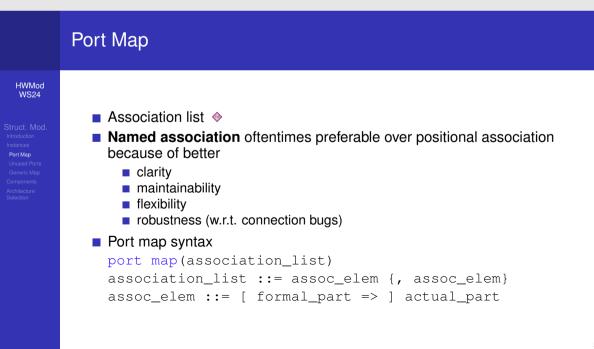

Formally the part inside the parentheses of the port map clause is referred to as an "association list". As its name suggests, its purpose is to associate or map an interface signal of an instance with some local signal or expression. This can be done using a positional mapping – like in the example on the previous slide – or using a named mapping.

Association list

### Furth Mod Name Struct Mod Instance Por Map Unused Fors Genetic Map Scheduch Por Map Drusted Fors Scheduch

−Structural Modeling └─Instances └─**Port Map**

Association list

Association oftentimes preferable over positional association

because of better

e darky

maintainabity

toxicity

robustness (w.r.t. connection bugs)

In comparison to positional association, named association increases readability and reduces the chance of errors, especially in designs with many signals or ports. By specifying each connection by name, the code becomes more self-explanatory, and modifications, such as adding, removing, or rearranging ports, can be made without affecting the order of other connections. Named association thus provides better clarity, maintainability, and flexibility, and is generally preferable to the positional variant.

−Structural Modeling └─Instances └─**Port Map**

Association is 4

Association is 4

Maned association of the first preferable over positional association

to device

analysis

material association

the device of the device

Syntactically the association list of a port clause looks very similar to an aggregate expression for records. If both positional and named associations are used in the same association list, then all positional associations must appear first. Hence, once a named association is used, the rest of the association list must only use named associations. However, although it supported by the standard, we strongly advise against mixing association styles when creating instances! Note that we will encounter association lists again, when we talk about function and procedure calls in an upcoming lecture. Here mixed association styles can sometimes be beneficial when dealing with default parameters of a subprogram. The formal part of a named association must refer to a port signal of the entity being instantiated. For port maps the actual part can be an expression containing local signals or constants.

## ─Structural Modeling □Instances □ Port Map - Example: Full Adder

OK, let's look at another code example. You should already know the full adder circuit from a previous lecture. Notice that the full adder can be broken down into two half adders and an "OR"-gate. Hence, we will now implement an architecture that contains two half adder instances.

#### Port Map - Example: Full Adder

#### HWMod WS24

```

1 entity fa is

2 port (

3 a, b, cin : in std_ulogic;

4 sum, cout : out std_ulogic

5 );

6 end entity;

```

#### —Structural Modeling └─Instances └─Port Map - Example: Full Adder

The two instances are named ha1 and ha2. The former one uses positional association in its port map, while the latter uses the named association style. Notice that, although the first port map is much more compact, it is much harder to understand to code without referring back to the half adder entity declaration. For, ha2 it is immediately clear what the inputs and outputs do. Further notice, how the or-gate producing the final carry-out signal is implemented as a concurrent signal assignment. This shows that instances, concurrent signal assignments as well as processes and other structures can be mixed in one architecture. Also recall that the sequence of statements is irrelevant for the semantics of the code. You might want to pause the video at this point, to really understand the shown circuit and code snippet.

#### Port Map - Example: Full Adder

#### HWMod WS24

```

2 port (

3 a, b, cin : in std_ulogic;

4 sum, cout : out std_ulogic

5 );

6 end entity;

```

```

architecture arch of fa is

signal x, y, z : std_ulogic;

3

begin

hal : entity work.ha

4

5

port map(a, b, x, y);

6

7

ha2 : entity work.ha

8

port map(

9

a => cin,

10

b => x,

cout => z,

12

sum => sum

13

);

14

15

cout <= y or z;

16 end architecture;

```

#### −Structural Modeling └─Instances └─**Unused Ports**

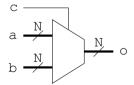

Oftentimes it is the case that not all interface signals of an instance are actually used or needed within the instantiating architecture. Reasons for that might be the modular design of components, where the interface is made to be more generic and reusable across different contexts. In such cases, signals may exist to accommodate various configurations, but not all configurations require every signal. Another reason could be that the design includes optional features, controlled by configuration parameters or generics, where only certain signals are used depending on how these options are set. In any case, the question arises how to deal with these situations in code. For that we have to make a distinction between inputs and outputs.

# Unused Ports

#### −Structural Modeling └─Instances └─**Unused Ports**

Unused outputs **B** Use copen keyword **b** Don't loave unconnected! 1 (1-1) 2 elspel a, b, c, w + els(\_loapsy 2 elspel a, b, c, w + els(\_loapsy 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + elspel a) 4 elspel a, b, c, w + el

Unused output ports should be clearly marked with the open keyword. While not strictly required by the VHDL language specification, this is good practice as it improves readability by making unconnected outputs explicit and helps prevent confusion. It also avoids potential warnings issued by some simulation or synthesis tools. In the example code, we instantiated a full adder but ignored the sum output since as our intent is in using it solely as a majority gate – a function that is implemented by the carry-output.

#### **Unused Ports** HWMod **WS24** Unused outputs Use open keyword Don't leave unconnected! Unused Ports 1 [...] 2 signal a, b, c, m : std\_ulogic; 3 begin 4 majority : entity work.fa 5 port map ( 6 a => a, 7 b => b, 8 c => c, 9 sum => open, -- not connected 10 cout => m 11 ); 12 [...]

#### −Structural Modeling └─Instances └─**Unused Ports**

| Unused outputs  Use open keyword  Don't leave unconnected! | Unused inputs     Connect to constant     If not connected      default value |

|------------------------------------------------------------|-------------------------------------------------------------------------------|

|                                                            |                                                                               |

|                                                            |                                                                               |

| z signal a, b, c, m s std_ulogicy                          | z signal a, b, sum, cout a std_ulogi-                                         |

| a begin                                                    | a begin                                                                       |

| a majority a estity work.fa                                | i half adder i entity work fa                                                 |

| s port map (                                               | s port map (                                                                  |

| <ol> <li>a -&gt; a.</li> </ol>                             | <ol> <li>a -&gt; a.</li> </ol>                                                |

| 7 h -> h.                                                  | 7 h -> h.                                                                     |

| a -> a,                                                    | a -> "0", constant                                                            |

| sum -> open, not connected                                 | 1 Aut -2 Aut.                                                                 |

| to cout -> m                                               | 10 cout -> cout                                                               |

| = 1)                                                       | = ))                                                                          |

| 12 []                                                      | 12 []                                                                         |

For unused inputs, we recommend assigning them a constant value, as demonstrated in the example code. It's also possible to use the <u>open</u> keyword or simply leave them unconnected. In this case, the port's default value - specified in the entity declaration - will be applied. If no default value is specified, a compilation error will be raised. However, for the same reason as already mentioned for outputs we strongly advise on using constant values.

|                                                                        | Unused Ports                                                                                                                                                                                          |                                                                                                                                                                                                             |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HWMod<br>WS24<br>Struct. Mod.<br>Introduction<br>Instances<br>Port Map | Unused outputs <ul> <li>Use open keyword</li> <li>Don't leave unconnected!</li> </ul>                                                                                                                 | Unused inputs<br>■ Connect to constant<br>■ If not connected → default value                                                                                                                                |

| Unused Ports<br>Generic Map<br>Components<br>Architecture<br>Selection | <pre>1 [] 2 signal a, b, c, m : std_ulogic; 3 begin 4 majority : entity work.fa 5 port map ( 6 a =&gt; a, 7 b =&gt; b, 8 c =&gt; c, 9 sum =&gt; open, not connected 10 cout =&gt; m 11 ); 12 []</pre> | <pre>1 [] 2 signal a, b, sum, cout : std_ulogic; 3 begin 4 half_adder : entity work.fa 5 port map ( 6 a =&gt; a, 7 b =&gt; b, 8 c =&gt; '0', constant 9 sum =&gt; sum, 10 cout =&gt; cout 11 ); 12 []</pre> |

#### −Structural Modeling └─Instances └─Generic Map

Generic map syntax generic map (association\_list)

Must appear before port map

Similar to how the ports of an instance are connected to local signals, there exists an analogous mechanism for generics in the form of the generic-map clause. The generic-map clause also takes an association list and, hence, also supports named and positional association.

## Generic Map WWMod WS24 Struct Mod. Wredwide Was Marked Parks Generic Map (association\_list) Therefore Map Sectors Arched Parks Generic Map (association\_list) Better Must appear before port map

#### -Structural Modeling Instances

Generic map syntax

generic map (association\_list)

Must appear before port map

Use named association and avoid the positional style

Using named association for generics provides the same benefits as for ports, such as improved clarity and reduced potential for errors.

#### Student Window Window

#### -Structural Modeling Instances

Generic map syntax generic map (association\_list) Must appear before port map Use named association and avoid the positional style Formal parts must be completime constants (generics cannot be connected to signals)

A major difference compared to mapping port signals is that the actual part of a generic association must always be a compile-time constant expression. This means it cannot depend on runtime data or dynamically changing values, such as signals. This ensures that the generic values are determined and fixed during simulation and synthesis. Oftentimes generics are mapped to generics of the instantiating architecture which allows to pass paramaters down through a design hierarchy

#### FUNDOD Windowski Vendowski Kaneski Kane

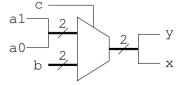

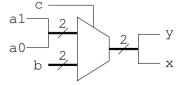

## ─Structural Modeling □Instances □Generic Map – Example: Multiplexer

Let's consider this generic two-to-one multiplexer, whose data width can be configured using the generic N. By now, the shown code snippet should be quite clear to you. However, you can pause the video and take some time to understand it.

#### Generic Map – Example: Multiplexer

HWMod WS24

```

1 entity mux is

generic (

2

3

N : positive

);

4

5

port (

c : in std_ulogic;

6

7

a : in std_ulogic_vector(N-1 downto 0);

b : in std_ulogic_vector(N-1 downto 0);

8

o : out std_ulogic_vector(N-1 downto 0)

9

10

);

11 end entity;

12

13 architecture arch of mux is

14 begin

15 o <= a when c = '0' else b;

16 end architecture;

```

-Structural Modeling -Instances Generic Map – Example: Multiplexer (cont'd)

Let's say we want to instantiate this entity in some other architecture with a data width of two.

#### Generic Map – Example: Multiplexer (cont'd)

#### HWMod WS24

```

[...]

1

signal c : std_ulogic;

2

signal a0, a1 : std_ulogic;

3

signal b : std_ulogic_vector(1 downto 0);

4

signal x, y : std_ulogic;

5

6 begin

7

mux_inst : entity work.mux

generic map (N => 2)

8

9

port map (

10

c => c,

11

a => a1 & a0,

12

b => b,

13

o(0) => x,

o(1) => y

14

15

);

[...]

16

```

Hence, we use a generic map clause that maps the generic N to the constant value two.

#### Generic Map – Example: Multiplexer (cont'd)

#### HWMod WS24

```

[...]

1

signal c : std_ulogic;

2

signal a0, a1 : std_ulogic;

3

signal b : std_ulogic_vector(1 downto 0);

4

signal x, y : std_ulogic;

5

6 begin

7

mux_inst : entity work.mux

generic map (N => 2)

8

9

port map (

10

c => c,

11

a => a1 & a0,

12

b => b,

13

o(0) => x,

o(1) => y

14

15

);

[...]

16

```

Now, the inputs a and b as well as the output o can be connected to std\_ulogic\_vector signals of length two.

#### Generic Map – Example: Multiplexer (cont'd)

#### HWMod WS24

```

[...]

1

signal c : std_ulogic;

2

signal a0, a1 : std_ulogic;

3

signal b : std_ulogic_vector(1 downto 0);

4

5

signal x, y : std_ulogic;

6 begin

mux_inst : entity work.mux

7

generic map (N => 2)

8

9

port map (

10

c => c,

11

a => a1 & a0,

12

b => b,

o(0) => x,

13

14

o(1) => y

15

);

[...]

16

```

$\begin{array}{c} 1 & 1 & \dots & 1 \\ 1 & \dots & 1 & 1 & 1 & 1 & \dots & 1 \\ 1 & \dots & 1 & 1 & 1 & \dots & 1 \\ 1 & \dots & 1 & 1 & \dots & 1 \\ 1 & \dots & 1 & \dots & 1 \\ 1 & \dots & 1 & \dots & 1 \\ 1 & \dots & 1 & \dots & 1 \\ 1 & \dots & 1 & \dots & 1 \\ 1 & \dots & 1 & \dots & 1 \\ 1 & \dots & 1 & \dots & 1 \\ 1 & \dots & 1 & \dots & 1 \\ 1 & \dots & 1 & \dots & 1 \\ 1 & \dots & 1 & \dots & 1 \\ 1 & \dots & 1 & \dots & 1 \\ 1 & \dots & 1 & \dots & 1 \\ 1 & \dots & 1 & \dots & 1 \\ 1 & \dots & 1 & \dots & 1 \\ 1 & \dots & 1 & \dots & 1 \\ 1 & \dots & 1 & \dots & 1 \\ 1 & \dots & 1 & \dots & 1 \\ 1 & \dots & 1 & \dots & 1 \\ 1 & \dots & 1 & \dots & 1 \\ 1 & \dots & 1 & \dots & 1 \\ 1 & \dots & 1 & \dots & 1 \\ 1 & \dots & 1 & \dots & 1 \\ 1 & \dots & 1 & \dots & 1 \\ 1 & \dots & 1 & \dots & 1 \\ 1 & \dots & 1 & \dots & 1 \\ 1 & \dots & 1 & \dots & 1 \\ 1 & \dots & \dots & 1 \\$

This example snippet also shows the flexibility of association lists – specifically that the formal and actual parts are not restricted to be simple identifiers.

#### Generic Map - Example: Multiplexer (cont'd)

#### HWMod WS24

```

[...]

1

signal c : std_ulogic;

2

signal a0, a1 : std_ulogic;

3

signal b : std_ulogic_vector(1 downto 0);

4

5

signal x, y : std_ulogic;

6 begin

7

mux_inst : entity work.mux

generic map (N => 2)

8

9

port map (

10

c => c,

11

a => a1 & a0,

b => b,

12

o(0) => x,

13

14

o(1) => y

);

15

[...]

16

```

Notice, that the input a is mapped to two single-bit signals a0 and a1 using the concatenation operator.

#### Generic Map – Example: Multiplexer (cont'd)

#### HWMod WS24

```

[...]

1

signal c : std_ulogic;

2

signal a0, a1 : std_ulogic;

3

signal b : std_ulogic_vector(1 downto 0);

4

signal x, y : std_ulogic;

5

6 begin

7

mux_inst : entity work.mux

generic map (N => 2)

8

9

port map (

10

c => c,

11

a => a1 & a0,

12

b => b,

13

o(0) => x,

o(1) => y

14

15

);

[...]

16

```

Moreover, the individual bits of output  $\circ$  are mapped separately to the local signals x and y.

#### Generic Map – Example: Multiplexer (cont'd)

#### HWMod WS24

```

[...]

1

signal c : std_ulogic;

2

signal a0, a1 : std_ulogic;

3

signal b : std_ulogic_vector(1 downto 0);

4

5

signal x, y : std_ulogic;

6 begin

mux_inst : entity work.mux

7

generic map (N => 2)

8

9

port map (

10

c => c,

11

a => a1 & a0,

12

b => b,

o(0) => x,

13

0(1) => y

14

15

);

[...]

16

```

#### -Structural Modeling Components

You have probably noticed that in all instantiation examples in this lecture, we had to specify more than just the name of the entity. In particular, we always had to explicitly state that we want to instantiate an entity using the entity keyword followed by the name of the library the entity resides in – in our case the default library "work" – and the actual name of the entity.

## Components FWMod Wsche Ratines Selection Image: Components

#### -Structural Modeling Components

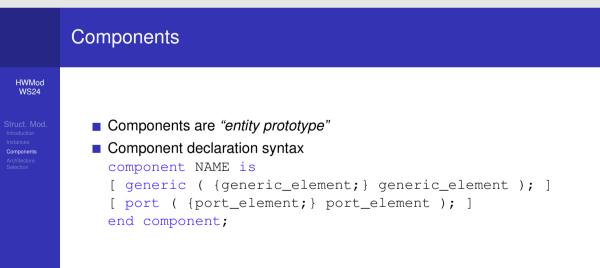

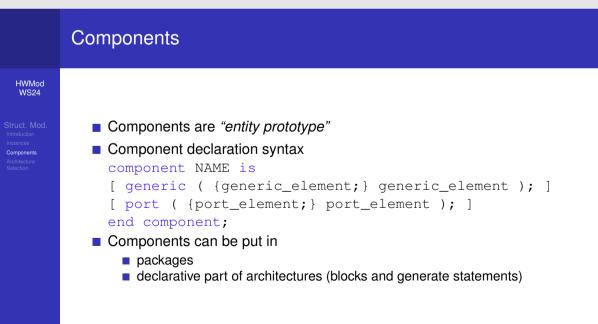

Components are "entity prototype"

This was necessary because we did not declare components to our entities. To draw a comparison to the C programming language, you can view a component as the prototype of an entity. The prototype contains only interface information, without providing any details about its internal implementation. Just as function prototypes in C allow you to reference functions before they are defined, component declarations in VHDL allow you to instantiate and reference entities in your design without knowing the full implementation at that point.

#### −Structural Modeling └─Components └─Components

B Components are 'entity prototype' B Component declaration syntax component NMMC is [ generic ( (generic\_slement;) generic\_slement ); [ port ( [port\_slement; ] port\_slement ); ] end component;

As shown in the formal syntax specification, entity and component declarations look quite similar. However, as we are only interested in the interface and not in any implementation details components do not have a declarative or statement part.

#### −Structural Modeling └─Components └─Components

component sue 'notip protopor' component decision pritar programment NUME is [percif ( [percif\_\_lement;] generic\_slement); ] [percif ( [percif\_\_lement;] pert\_slement); ] [percif ( [percif\_\_lement]; pert\_slement); ] [component can be pit in = besizes = decision per of architectures (block and generate statements)

In the C programming language the function prototypes are usually put into header files, while their implementation is kept separate in some C file. In VHDL you can do a similar thing, by putting components in packages and include them elsewhere in you design. However, it is also possible to declare them directly in declarative parts of architectures.

#### -Structural Modeling └-Components └-**Components (cont'd)**

Instantiation example

ErR(p; i; i; i; part map (...);

Component i; i; part map (...);

Component (map(b)); i; cancent i; part map (...);

Modulent, abstaction and separation of concerns

Compliant on early of an analable

Amad manguage designs

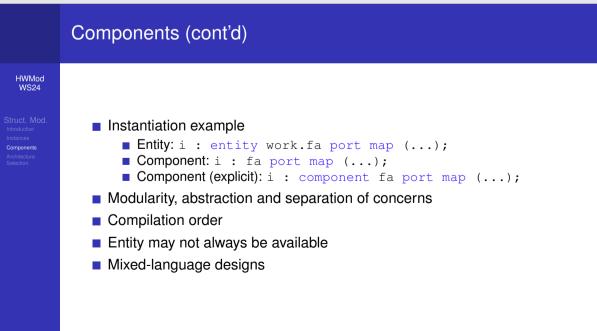

Now the question may arise, why even bother with components? As shown in the code examples the component instantiation syntax is a little simpler and more compact. Generally, the same arguments as for structuring C programs into header and source files apply here. Components in VHDL, like functions and modules in C, help break down complex designs into smaller, more manageable parts, promoting modularity and reusability and a separation of concerns. Moreover, they help to relax constraints on the compilation order and can, hence, improve compilation and synthesis speeds. Sometimes, it can also be the case that you don't have access to a modules' implementation – neither its entity nor its architecture. This can, for example, occur when you're working with precompiled IP cores or third-party libraries provided by FPGA vendors or other companies. In such cases, you are given a black box view of the module, where the internal workings are hidden, but the external interface is available in the form of a component declaration. You can again compare this to the situation in software development where you have a precompiled library, without access to its source code. In both cases, you are provided with the interface – in software, typically in the form of a header file – that describes the inputs and outputs, or functions and their arguments. Components are also needed when you are working with mixed-language designs – for example when you mix VHDL and Verilog in a single project.

#### −Structural Modeling └─Architecture Selection └─**Architecture Selection**

Multiple different architectures possible for a single entity

+ How to select one?

Two possibilities

Spacify architecture, when an entity is instantiated

Caution: This does not work for componental

to Configurations

As we have discussed in a previous lecture, an entity can have multiple different architectures. So you might ask yourself, how we can select a particular one when creating an instance of a module. VHDL offers two possibilities to do that.

#### Contract Model Workstein Contract Model Workstein Contract Model Workstein Contract Model Workstein Contract Model Contract

#### −Structural Modeling └─Architecture Selection └─Entity Instantiations

When creating an instance of an entity, it is possible to specify the name of the architecture that should be used after the entity name in parentheses. Note however, that this only works for entity instantiation and not for components. In the example code on the left we have declared a simple entity with two inputs and one output called "mystery". It has two different architectures, a1 and a2, implementing the behavior of an "XOR" and an "and"-gate, respectively.

#### **Entity Instantiations**

HWMod WS24

Struct. Mod. Introduction Instances Components Architecture Selection Entity Instantiations

onfigurations

```

1 entity mystery is

2 port (

3 a, b : in std_ulogic;

x : out std_ulogic

4

5);

6 end entity;

7

8 architecture al of mystery is

9 begin

10 x \leq a and b;

11 end architecture;

12

13 architecture a2 of mystery is

14 begin

15 x <= a xor b;

16 end architecture;

```

#### −Structural Modeling └─Architecture Selection └─Entity Instantiations

| <pre>i extity mystery is    port (</pre>                                                                                                                                                                                                                          | <pre>t estity ha is post (     a, b is std_ulogic;     sam, cout : out std_ulogic     b;     sed estity; </pre>                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| a suchitecture at of spatery is<br>a begin<br>to $x \leftarrow a$ and by<br>to $x \leftarrow a$ and by<br>to an architecture,<br>to<br>to architecture at of spatery is<br>to begin<br>to $x \leftarrow a$ sor by<br>to end architecture,<br>to end architecture, | 7<br>8 architecture arch of ha is<br>8 begin<br>10 and_gate : entry work.wystery(al<br>11 port map (s, b, court);<br>12 aor_gate : entry work.wystery(al<br>13 port map (s, b, sum);<br>18 end architecture;<br>19 |

On the right side we can now see how to use this gate to implement the half adder circuit, we have already seen on a previous slide. Notice how the architecture names appear next to name of the entity names.

#### **Entity Instantiations**

HWMod WS24

Struct. Mod. Introduction Instances Components Architecture Selection Entity Instantiations

onfigurations

```

1 entity mystery is

1 entity ha is

2 port (

2 port (

3 a, b : in std_ulogic;

a, b : in std_ulogic;

3

x : out std_ulogic

4

4

sum, cout : out std_ulogic

5);

5

);

6 end entity;

6 end entity:

7

7

8 architecture al of mystery is

8 architecture arch of ha is

9 begin

9 begin

10 x \leq a and b;

10 and_gate : entity work.mystery(al)

11 end architecture;

11 port map (a, b, cout);

12

12

13 architecture a2 of mystery is

13 xor_gate : entity work.mystery(a2)

14 begin

14 port map (a, b, sum);

15 x <= a xor b;

15 end architecture;

16 end architecture;

```

#### └─Structural Modeling └─Architecture Selection └─Configurations

| The other possibility to select between architectures is via the use of an VHDL language feature called configurations.           |

|-----------------------------------------------------------------------------------------------------------------------------------|

| lowever, we don't want to go into too much detail about this feature as its syntax is a little involved. It suffices, if you know |

| hat a configuration, can - among other things - select a particular architecture for a particular instance in a design, without   |

| he need to change the architecture in which this instance is created. Let us close this lecture with a simple practical           |

| example for a configuration, that we will also encounter in the exercise part of this course. For tasks that must be loaded       |

| nto the FPGA board you will have a top-level entity named debug-top, which contains two instances - the instance of the           |

| ser-top design and the debug-core, which provides some debugging capabilities. The figure on the right illustrates this           |

| lesign hierarchy. The user-top design has a fixed entity specification, and you will have to implement different architectures    |

| or the various tasks of the exercise sheet. Since we don't want to always change the debug-top architecture when we want          |

| o switch between different architectures for the individual tasks we can use a configuration. The code snippet on the left of     |

| he slide shows how this can look like. It creates a configuration named debug-top-conf for the debug-top entity, which has        |

| single architecture named debug-top-arch. For this architecture it then specifies that the instance named user-top-inst of        |

| he user-top entity shall use the arch-A architecture. Now, to change the architecture we only have to change line 4 of our        |

| onfiguration.                                                                                                                     |

|                                                                                                                                                  | Configurations                                                                                                                                                                                            | 26                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HWMod<br>WS24<br>Struct. Mod.<br>Introduction<br>Instances<br>Components<br>Architecture<br>Selection<br>Entity Instantiations<br>Configurations | <pre>1 configuration dbg_top_conf of dbg_top is<br/>2 for dbg_top_arch<br/>3 for user_top_inst : user_top<br/>4 use entity user_top(arch_A);<br/>5 end for;<br/>6 end for;<br/>7 end configuration;</pre> | dbg_top<br>dbg_core_inst : dbg_core<br>debugging logic for<br>the user top design<br>user_top_inst : user_top<br>multiple architectures<br>arch_A,, arch_Z |

|                                                                                                                                                  |                                                                                                                                                                                                           |                                                                                                                                                            |

gJop dbg.core.inst : dbg.core debugging logic for the user top design

user,top,inst : user,top multiple architectures arch.A. ..., arch.Z Thank you for listening! We recommend you to immediately take the self-check test in TUWEL, to see if you understood the material presented in this lecture.

Struct. Mod. Introduction Instances Components Architecture Selection Entity Instantiatio

## Lecture Complete!

Modified: 2025-03-12, 16:33 (21636bb)