# Hardware Modeling [VU] (191.011)

## – WS25 –

### Structural Modeling

Florian Huemer & Sebastian Wiedemann & Dylan Baumann

WS 2025/26

# Introduction

HWMod

WS25

Struct. Mod.

Introduction

Instances

Components

Architecture

Selection

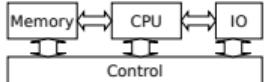

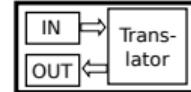

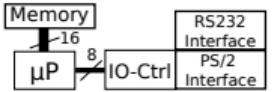

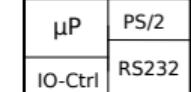

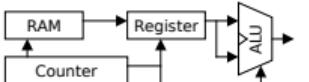

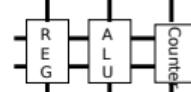

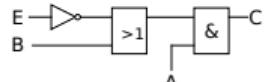

|                               | Behavior                                                                      | Structure                                                                          | Geometry                                                                            |

|-------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| System Level                  | Inputs : Keyboard<br>Output: Display<br>Function: .....                       |  |  |

| Algorithmic Level             | while input<br>read English text<br>translate to German<br>output German Text |  |  |

| Register Transfer Level (RTL) | if A='1' then<br>B:= B+1<br>else<br>B:= B<br>end if                           |  |  |

| Logic Level                   | D = NOT E<br>C = (D OR B) AND A                                               |  |  |

| Circuit Level                 | $\frac{dU}{dt} = R \frac{dI}{dt} + \frac{1}{C} + L \frac{d^2I}{dt^2}$         |  |  |

# Introduction (cont'd)

HWMod

WS25

Struct. Mod.

Introduction

Instances

Components

Architecture

Selection

## Structural Modeling

Create complex modules by combining and interconnecting (simpler) sub-modules.

## Top-Level Design/Entity

The design unit (entity) that sits on highest layer of a hierarchical hardware design.

## Unit Under Test (UUT)

The module instantiated in a testbench and whose behavior is verified.

# Creating Instances – Example: Half Adder

HWMod

WS25

Struct. Mod.

Introduction

Instances

Port Map

Unused Ports

Generic Map

Components

Architecture

Selection

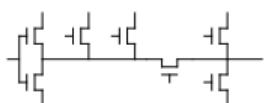

```

1 entity xor_gate is

2 port (

3   a, b : in std_uleogic;

4   x : out std_uleogic

5 );

6 end entity;

7

8 architecture arch of xor_gate is

9 begin

10  x <= a xor b;

11 end architecture;

```

```

1 entity and_gate is

2 port (

3   a, b : in std_uleogic;

4   x : out std_uleogic

5 );

6 end entity;

7

8 architecture arch of and_gate is

9 begin

10  x <= a and b;

11 end architecture;

```

# Creating Instances – Example: Half Adder

HWMod

WS25

Struct. Mod.

Introduction

Instances

Port Map

Unused Ports

Generic Map

Components

Architecture

Selection

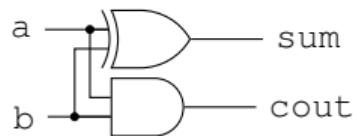

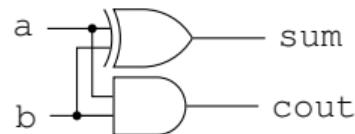

```

1 entity ha is

2 port (

3     a, b : in std_uleogic;

4     sum, cout : out std_uleogic

5 );

6 end entity;

7

8 architecture arch of ha is

9 begin

10    and_gate_inst : entity work.and_gate

11    port map (a, b, cout);

12

13    xor_gate_inst : entity work.xor_gate

14    port map (a, b, sum);

15 end architecture;

```

- Instances → statement part

- Two instantiation statements

- Positional association

- Inputs must be readable, outputs writable

# Port Map

HWMod

WS25

Struct. Mod.

Introduction

Instances

Port Map

Unused Ports

Generic Map

Components

Architecture

Selection

- Port map syntax

```

port map (association_list)

```

- Part in parentheses → Association list

- Named and positional associations possible

- **Named association** oftentimes preferable over positional association because of better

- clarity

- maintainability

- flexibility

- robustness (w.r.t. connection bugs)

- Association list syntax

```

association_list ::= assoc_elem {, assoc_elem}

```

```

assoc_elem ::= [formal_part => ]actual_part

```

- Don't mix association styles in port maps

# Port Map - Example: Full Adder

HWMod

WS25

Struct. Mod.

Introduction

Instances

Port Map

Unused Ports

Generic Map

Components

Architecture

Selection

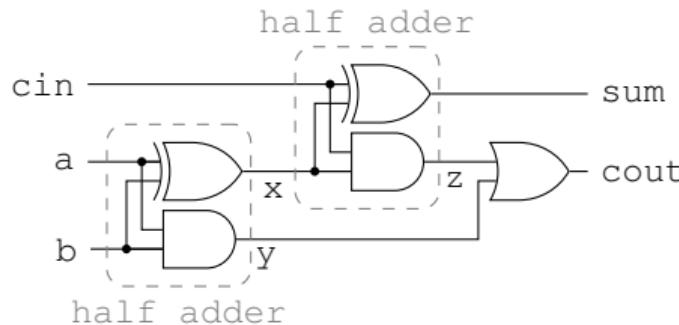

```

1 entity fa is

2 port (

3   a, b, cin : in std_ulogic;

4   sum, cout : out std_ulogic

5 );

6 end entity;

```

```

1 architecture arch of fa is

2 signal x, y, z : std_ulogic;

3 begin

4   hal : entity work.ha

5   port map(a, b, x, y);

6

7   ha2 : entity work.ha

8   port map(

9     a => cin,

10    b => x,

11    cout => z,

12    sum => sum

13  );

14

15  cout <= y or z;

16 end architecture;

```

# Unused Ports

HWMOD

WS25

Struct. Mod.

Introduction

Instances

Port Map

Unused Ports

Generic Map

Components

Architecture

Selection

## Unused outputs

- Use `open` keyword

- Don't leave unconnected!

```

1 [...]

2 signal a, b, c, m : std_ulogic;

3 begin

4 majority : entity work.fa

5 port map (

6 a => a,

7 b => b,

8 c => c,

9 sum => open, -- not connected

10 cout => m

11 );

12 [...]

```

## Unused inputs

- Connect to constant

- If not connected → default value

```

1 [...]

2 signal a, b, sum, cout : std_ulogic;

3 begin

4 half_adder : entity work.fa

5 port map (

6 a => a,

7 b => b,

8 c => '0', -- constant

9 sum => sum,

10 cout => cout

11 );

12 [...]

```

# Generic Map

HWMod

WS25

Struct. Mod.

Introduction

Instances

Port Map

Unused Ports

**Generic Map**

Components

Architecture

Selection

- Generic map syntax

```

generic map (association_list)

```

- Must appear before port map

- Use named association and avoid the positional style

- Formal parts must be compile-time constants (generics cannot be connected to signals)

# Generic Map – Example: Multiplexer

HWMod

WS25

Struct. Mod.

Introduction

Instances

Port Map

Unused Ports

**Generic Map**

Components

Architecture

Selection

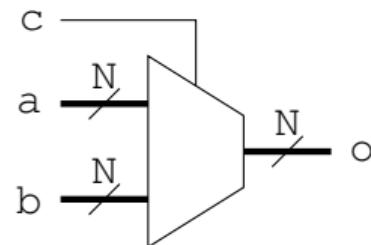

```

1 entity mux is

2 generic (

3   N : positive

4 );

5 port (

6   c : in std_ulogic;

7   a : in std_ulogic_vector(N-1 downto 0);

8   b : in std_ulogic_vector(N-1 downto 0);

9   o : out std_ulogic_vector(N-1 downto 0)

10 );

11 end entity;

12

13 architecture arch of mux is

14 begin

15   o <= a when c = '0' else b;

16 end architecture;

```

# Generic Map – Example: Multiplexer (cont'd)

HWMod

WS25

Struct. Mod.

Introduction

Instances

Port Map

Unused Ports

Generic Map

Components

Architecture

Selection

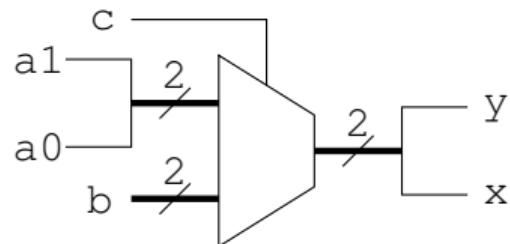

```

1  [...]

2  signal c : std_uleogic;

3  signal a0, a1 : std_uleogic;

4  signal b : std_uleogic_vector(1 downto 0);

5  signal x, y : std_uleogic;

6 begin

7  mux_inst : entity work.mux

8  generic map (N => 2)

9  port map (

10    c => c,

11    a => a1 & a0,

12    b => b,

13    o(0) => x,

14    o(1) => y

15  );

16  [...]

```

# Components

- Components are “*entity prototype*”

- Component declaration syntax

```

component NAME is

[ generic ( {generic_element;} generic_element );

[ port ( {port_element;} port_element );

end component;

```

- Components can be put in

- packages

- declarative part of architectures (blocks and generate statements)

# Components (cont'd)

## ■ Instantiation example

- Entity: `i : entity work.fa port map (...);`

- Component: `i : fa port map (...);`

- Component (explicit): `i : component fa port map (...);`

- Modularity, abstraction and separation of concerns

- Compilation order

- Entity may not always be available

- Mixed-language designs

# Architecture Selection

HWMod

WS25

Struct. Mod.

Introduction

Instances

Components

Architecture

Selection

Entity Instantiations

Configurations

- Multiple different architectures possible for a single entity

⇒ How to select one?

- Two possibilities

- Specify architecture, when an **entity** is instantiated

**Caution:** This does not work for components!

- Configurations

# Entity Instantiations

HWMod

WS25

Struct. Mod.

Introduction

Instances

Components

Architecture

Selection

Entity Instantiations

Configurations

```

1 entity mystery is

2 port (

3   a, b : in std_ulogic;

4   x : out std_ulogic

5 );

6 end entity;

7

8 architecture a1 of mystery is

9 begin

10  x <= a and b;

11 end architecture;

12

13 architecture a2 of mystery is

14 begin

15  x <= a xor b;

16 end architecture;

```

```

1 entity ha is

2 port (

3   a, b : in std_ulogic;

4   sum, cout : out std_ulogic

5 );

6 end entity;

7

8 architecture arch of ha is

9 begin

10  and_gate : entity work.mystery(a1)

11  port map (a, b, cout);

12

13  xor_gate : entity work.mystery(a2)

14  port map (a, b, sum);

15 end architecture;

```

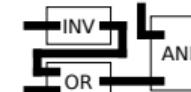

# Configurations

HWMod

WS25

Struct. Mod.

Introduction

Instances

Components

Architecture

Selection

Entity Instantiations

Configurations

```

1 configuration dbg_top_conf of dbg_top is

2   for dbg_top_arch

3     for user_top_inst : user_top

4       use entity user_top(arch_A);

5     end for;

6   end for;

7 end configuration;

```

dbg\_top

dbg\_core\_inst : dbg\_core

debugging logic for

the user top design

user\_top\_inst : user\_top

multiple architectures

arch\_A, ..., arch\_Z

# Lecture Complete!