-Sequential Circuit Elements in VHDL

This lecture covers how sequential circuit elements, such as flip-flops and latches, are modeled in VHDL, how they differ and how to deal with them in simulation.

Seq. Elem. Introduction D Latches D Filp-Flop LFSR

#### Hardware Modeling [VU] (191.011) - WS24 -

Sequential Circuit Elements in VHDL

Florian Huemer & Sebastian Wiedemann & Dylan Baumann

WS 2024/25

Modified: 2025-03-12, 16:32 (21636bb)

#### -Sequential Circuit Elements in VHDL Introduction

Combinational logic cannot retain any data

So far, we have only dealt with purely combinational VHDL designs. That is, circuits that compute outputs based solely on their current inputs, without any memory or feedback. These circuits do not store state information, meaning their outputs are immediately and directly influenced by changes in inputs, with no dependence on previous input values or timing. However, as we have learned in the lecture about synchronous design, sequential circuits require memory elements, allowing them to store and utilize past states or input values. In synchronous designs, the circuit behavior is coordinated by a clock signal, controlling when state changes occur in memory elements such as latches and flip-flops. In this lecture we will show you how to implement these memory elements in VHDL and how to use them in a circuit.

## —Sequential Circuit Elements in VHDL Introduction Introduction

Both latches and flip-flops are storage elements that hold a single bit of data. An upcoming lecture will discuss larger memory elements, such as RAMs, ROMs and FIFOs.

#### Introduction

HWMod WS24

Seq. Elem. Introduction Latches vs. FFs Reset Signal Active Signal Level D Latches D Flip-Flop LFSR

- Combinational logic cannot retain any data

- Latches and flip-flops are single-bit storage elements

## —Sequential Circuit Elements in VHDL Untroduction Untroduction

Combinational logic cannot retain any data

Latches and flip-flops are single-bit storage elements

Operation principle

Latbres: losel-sensitive

Flip-flops: edge-triggered

The major difference between latches and flip-flops is how they react to their input signals and what events cause them to update their internal state. While latches operate based on signal levels, flip-flops only react to rising or falling clock edges.

#### Introduction

#### HWMod WS24

Seq. Elem. Introduction Latches vs. FFs Reset Signal Active Signal Leve D Latches D Flip-Flop

- Combinational logic cannot retain any data

- Latches and flip-flops are single-bit storage elements

- Operation principle

- Latches: level-sensitive

- Flip-flops: edge-triggered

## —Sequential Circuit Elements in VHDL Untroduction Untroduction

Combinational logic cannot retain any data

Latches and tip-flops are single-bit storage elements

Operation principle

Latches: lovel-sensitive

Fip-flops: dega-triggered

Latches: can be problematic in synchronous designal

The level-sensitive nature of latches makes them somewhat problematic in synchronous designs, as an upcoming lecture will discuss. Thus, they must be strictly avoided in designs during this course. Nevertheless, it is important to cover both concepts as they represent fundamental building blocks of digital systems and to understand the potentially problematic aspects of them.

## Sec Form Model Model

#### —Sequential Circuit Elements in VHDL └─ Introduction └─ Introduction

Combinational logic cannot retain any data

Lathers and fip-forgs are single-bit storage elements

Gonzation principale

Lathers: Invelsemative

Lathers: Invelsemative

Lathers: Can be problematic in synchronous designs!

Common Types

Lathers: RR, TO

Pip-forgs: LK, T, D

You might have already learned in other courses, that there exists a range of latches and flip-flops, such as RS or D latches, and JK, T or D flip-flops.

# Introduction Wind Sector Wind Wind And Sector And Sector Charter Charter

—Sequential Circuit Elements in VHDL

Untroduction

Untroduction

Combinational logic cannot readin any data

Latabas and rights are a nagle bit storage elements

Latabas and rights are single bit storage elements

Latabas can bit elements

Latabas can be problematic in synchronicus designel

Latabas can be consecutive to the problematic in synchronicus designed

Latabas can be consecutive to the problematic in synchronicus designed

Latabas can be consecutive to the problematic in synchronicus designed

Latabas can be consecutive to the problematic in synchronicus designed

Latabas can be consecutive to the problematic in synchronicus designed

Latabas can be consecutive to the problematic in synchronicus designed

Latabas can be consecutive to the problematic in synchronicus designed

Latabas can be consecutive to the problematic in synchronicus designed

Latabas can be consecutive to the problematic in synchronicus designed

Latabas can be consecutive to the problematic in synchronicus designed

Latabas can be consecutive to the problematic in synchronicus designed

Latabas can be consecutive to the problematic in synchronicus designed

Latabas can be consecutive to the problematic in synchronicus designed

Latabas can be consecutive to the problematic in synchronicus designed

Latabas can be consecutive to the problematic in synchronicus designed

Latabas can be consecutive to the problematic in synchronicus designed

Latabas can be consecutive to the problematic in synchronicus designed

Latabas can be consecutive to the problematic in synchronicus designed

In this course only the D-type versions are of importance - D standing for data.

# Introduction Figure 2 Seq. Floring <t

Sequential Circuit Elements in VHDL

Introduction

Introduction (cont'd)

OK, let's start with some definitions.

#### Introduction (cont'd)

HWMod WS24

Seq. Elem. Introduction Latches vs. FFs Reset Signal Active Signal Leve D Latches D Flip-Flop

### —Sequential Circuit Elements in VHDL Introduction Introduction (cont'd)

D latches are level-sensitive. They transfer the data on the input (D) to the output (O) when enabled and retain the data when disabled.

A D latch is a level-sensitive single-bit storage device featuring an enable input. Whenever this input is active, the latch continuously transfers the signal level on its input D to its output Q. In this state the latch is also referred to as open, enabled, or transparent, as from the point of view of the input it appears as though the signal passes directly through to the output. When the enable input is inactive, the latch holds the last input value. This is referred to as closed, disabled, or opaque.

#### Introduction (cont'd)

#### HWMod WS24

Seq. Elem. Introduction Latches vs. FFs Reset Signal Active Signal Level: D Latches D Flip-Flop LFSR

#### D Latch

D latches are level-sensitive. They transfer the data on the input (D) to the output (Q) when enabled and retain the data when disabled.

### —Sequential Circuit Elements in VHDL Untroduction Untroduction (cont'd)

1 Etch blackba ze level-sensitive. They transfer the data on the input (D) to the upput (Q) when enabled and retain the data when disabled.

FIP Exp FIP Exp FIP Exp FIP Exp FIP Exp zended on the input (D) at a peofile clock edge, transfer it to the output (Q) and hold it until the next edge.

D flip-flops on the other hand only capture their input signal at single moments in time, marked by rising or falling transitions of a clock signal. During all other times the input signals can not affect the output of a D flip-flop. The specific clock edge the flip-flop reacts to is referred to as the active clock edge. Typically, the rising edge is used for this purpose. We will therefore only use this variant in this course.

#### Introduction (cont'd)

#### HWMod WS24

Seq. Elem. Introduction Latches vs. FFs Reset Signal Active Signal Levels D Latches D Filip-Flop LFSR

#### D Latch

D latches are level-sensitive. They transfer the data on the input (D) to the output (Q) when enabled and retain the data when disabled.

#### D Flip-Flop

D flip-flops are edge-triggered. They capture the data on the input (D) at a specific clock edge, transfer it to the output (Q) and hold it until the next edge.

## —Sequential Circuit Elements in VHDL Untroduction Untroduction (cont'd)

O techs D latches ar level-sensitive. They transfer the data on the input (b) to the output (b) when called and r train the data when disabled. D Fig.Figs are displayed by the output (b) and the output (b) at a specific color sign, transfer it. They capture the data on the input (b) at a specific color sign, transfer it. They capture the data on the input (b) at a specific color sign, transfer it. They capture the data on the input (b) at a specific color sign. They capture the data on the input (b) at a specific color sign. They capture the data on the input (b) at a specific color sign. They capture the data on the input (b) at specific color sign. They capture the data on the input (b) at the data that logically being together.

Finally, let us define the term register, as it is also important in the context of storage elements. A register is a set of single-bit storage elements – usually flip-flops – that are triggered by the same clock signal and work in unison to store multiple bits of data that logically belong together.

#### Introduction (cont'd)

#### HWMod WS24

Seq. Elem. Introduction Latches vs. FFs Reset Signal Active Signal Levels D Latches D Flip-Flop LFSR

#### D Latch

D latches are level-sensitive. They transfer the data on the input (D) to the output (Q) when enabled and retain the data when disabled.

#### D Flip-Flop

D flip-flops are edge-triggered. They capture the data on the input (D) at a specific clock edge, transfer it to the output (Q) and hold it until the next edge.

#### Register

Registers are collections of D flip-flops (latches) that hold data that logically belong together.

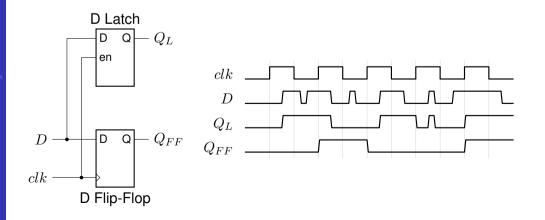

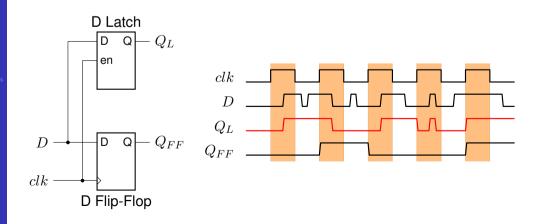

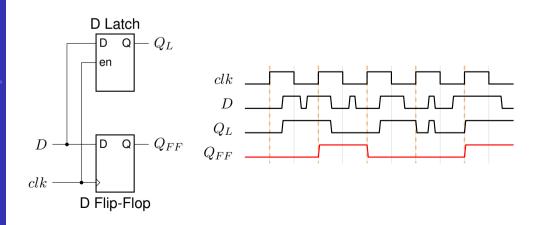

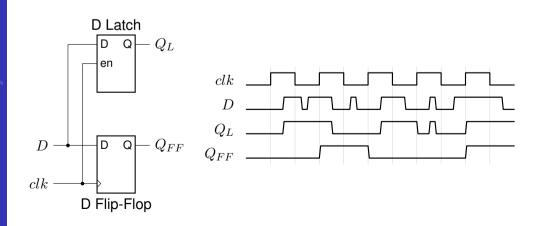

It is crucial that you really understand the difference between latches and flip-flops. Hence, consider this simple demo circuit consisting of a D latch and a D flip-flop. Both storage elements are connected to the same input signal D. The signal used to clock the flip-flop (clk) is used as the enable signal for the D latch.

# Provide<br/>Wind<br/>Wind<br/>Seq. Fire<br/>Peer Signal Lacters<br/>D Tarbers<br/>D Tarbers<br/>D

|--|

The timing diagram on the right side of the slide shows how the two storage elements react to the same input signals.

#### D Latches vs. D Flip-Flop

HWMod WS24

Seq. Elem. Introduction Latches vs. FFs Reset Signal Active Signal Level D Latches D Flip-Flop

Let's first consider the D latch. As we know from the previous slide it is transparent when the enable-signal is active. In our case this is during the high period of the clock, which is highlighted in the timing diagram. Notice that during these periods the output signal  $Q_L$  directly follows the input signal D. During the low-phase,  $Q_L$  is kept at the last value it had during the high period – changes of D during this phase have no effect.

#### D Latches vs. D Flip-Flop

HWMod WS24

Ceq. Elem. Introduction Latches vs. FFs Reset Signal Active Signal Level D Latches D Flip-Flop

For the D flip-flop only the rising clock edges are relevant. Only at these points in time D is captured and transferred to  $Q_{FF}$ . For the rest of the time the value of D is completely irrelevant.

#### D Latches vs. D Flip-Flop

HWMod WS24

Ceq. Elem. Introduction Latches vs. FFs Reset Signal Active Signal Level D Latches D Flip-Flop

Please, do not continue watching this lecture if this paramount difference is not clear to you at this point! If necessary, pause the video to really understand the shown timing diagram.

#### D Latches vs. D Flip-Flop

HWMod WS24

Seq. Elem. Introduction Latches vs. FFs Reset Signal Active Signal Level D Latches D Flip-Flop

#### —Sequential Circuit Elements in VHDL └─Introduction └─Reset Signal

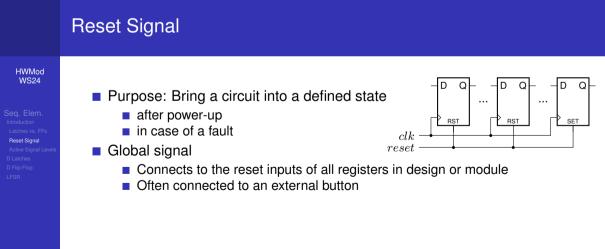

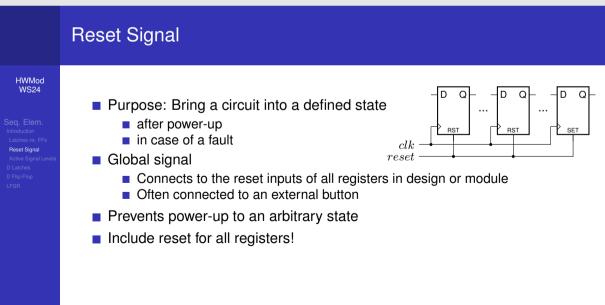

Most of the time in digital circuit design we want the storage elements to be initialized with a specific value upon power-up or when the circuit entered a faulty state from which we cannot recover by other means. This is the purpose of the reset signal.

## HWMod W24 Seq. Eler. In Case of a fault Marken Signal Water Signal Kater S

#### —Sequential Circuit Elements in VHDL └─ Introduction └─ Reset Signal

Like the clock, the reset is also a global signal that is usually connected to all storage elements in a design or module. On many chips the reset is a physical external pin that can, for example, be connected to a push button.

#### ─Sequential Circuit Elements in VHDL └─Introduction └─Reset Signal

The reset signal ensures that all storage elements are set to a predefined value, allowing the system to start from a known, stable state. A latch or flip-flop without a reset can power-up to an arbitrary value. Usually this is undesired, which is why it is good practice to reset all sequential elements, even if you consider it unnecessary. This also minimizes the potential for divergence between the behavior of the simulation and hardware.

#### 4

#### —Sequential Circuit Elements in VHDL └─ Introduction └─ Reset Signal

The typical reset value for storage elements is zero. However, this is not a strict rule, as sometimes it is also necessary to initialize storage elements to one. As shown by the right-most flip-flop in the drawing, we will mark flip-flops and latches whose reset value is one by labelling their reset inputs with SET instead of RST.

#### **Reset Signal** HWMod **WS24** Q Purpose: Bring a circuit into a defined state after power-up RST RST in case of a fault clkReset Signal Global signal resetConnects to the reset inputs of all registers in design or module Often connected to an external button Prevents power-up to an arbitrary state Include reset for all registers! Typical reset value is zero/low (sometimes different values are necessary)

#### —Sequential Circuit Elements in VHDL └─ Introduction └─ Reset Signal

Note that testbenches must always start by activating the reset, bringing the UUT into a defined state before applying test stimuli. While the reset is active all input signals to the UUT should also be set to defined values such that when the reset signal is released the design only sees valid input values.

#### **Reset Signal** HWMod **WS24** Purpose: Bring a circuit into a defined state after power-up RST RST in case of a fault clkReset Signal resetGlobal signal Connects to the reset inputs of all registers in design or module Often connected to an external button Prevents power-up to an arbitrary state Include reset for all registers! Typical reset value is zero/low (sometimes different values are necessary) Testbenches should always activate the UUT's reset upon startup

## -Sequential Circuit Elements in VHDL └─Introduction └─Active Signal Levels

A signal is considered active-high (low) when a high (low) logic level activat the signal or causes the intended action to occur.

Before we look at some VHDL code examples we have to introduce the important concept of active signal levels, referring to the specific logic level at which a signal is considered "active" or "asserted". In binary digital systems, signals can either be active-high or active-low. An active-high signal is active when it is at a logical one, typically represented by a high voltage level. Conversely, an active-low signal is considered active when its logical value is zero.

#### Active Signal Levels

#### HWMod WS24

Seq. Elem. Introduction Latches vs. FFs Reset Signal Active Signal Levels D Latches D Flip-Flop

#### Active Signal Levels

A signal is considered active-high (low) when a high (low) logic level activates the signal or causes the intended action to occur.

#### ─Sequential Circuit Elements in VHDL └─Introduction └─Active Signal Levels

To clearly distinguish active-low from active-high signals, we mark signals in circuit diagrams with a horizontal bar above the signal name and identifiers in source code with the suffix \_n.

#### **Active Signal Levels**

#### HWMod WS24

Seq. Elem. Introduction Latches vs. FFs Reset Signal Active Signal Levels D Latches D Flip-Flop LFSR

#### Active Signal Levels

A signal is considered active-high (low) when a high (low) logic level activates the signal or causes the intended action to occur.

- Notation for active-low signals:

- Circuit diagrams: a bar above the signal name (e.g., en)

- Code: the suffix \_n (e.g., en\_n)

−Sequential Circuit Elements in VHDL └─Introduction └─Active Signal Levels

Action Sorgenia Levide Assignal is considered active high (low) when a high (low) logic level activates the signal or causes the interned action to occur. I behavior to retroit be signalized I behavior to retroit be signalized I cost the signalized (low of the signalized (low of the signalized I cost the signalized (low of the signalized

The first time you will come into touch with an active-low signal is the reset signal. In digital designs the reset is often implemented in an active-low way, as this comes with several benefits. This design choice ensures that the system starts in a predictable state during power-up, as logic lines tend to default to low voltage, often called ground. Additionally, active-low resets are more robust in noisy environments, because electrical interference is less likely to falsely trigger a low signal than a high one. These characteristics, combined with the historical adoption of active-low conventions in TTL and CMOS technologies, make it a reliable practice and industry-standard. We will therefore exclusively use active-low resets, referring to this signal as res\_n. With that being said, we have everything we need to implement our first D latch in VHDL. We start with the latch as it is arguably the simpler state holding element.

#### Active Signal Levels

#### HWMod WS24

Seq. Elem. Introduction Latches vs. FFs Reset Signal Active Signal Levels D Latches D Filip-Flop

#### Active Signal Levels

A signal is considered active-high (low) when a high (low) logic level activates the signal or causes the intended action to occur.

- Notation for active-low signals:

- Circuit diagrams: a bar above the signal name (e.g., en)

- Code: the suffix \_n (e.g., en\_n)

- Active-low resets

- Noise immunity

- Power-up default

- Widely adopted in industry for reliability and compatibility

- Our naming convention: res\_n.

#### ─Sequential Circuit Elements in VHDL └─D Latches └─D Latches

| d D Q q<br>en en | <pre>t estity distch is post {     d i in std_ulogic;     e e i in std_ulogic;     q i out std_ulogic     b; }</pre> |

|------------------|----------------------------------------------------------------------------------------------------------------------|

|                  | 7 end entity;                                                                                                        |

The entity declaration of a D latch is quite straight-forward. We need two inputs d and en as well as a single output q.

#### **D** Latches HWMod **WS24** 1 entity dlatch is D Q q d -2 port ( en d : in std\_ulogic; en -3 D Latches en : in std\_ulogic; 4 5 q : out std\_ulogic 6 ); 7 end entity;

−Sequential Circuit Elements in VHDL □ D Latches □ D Latches

1 #2fity distch is 2 post ( 3 d : in std\_ulogic) 5 q : det std\_ulogic) 5 q : det std\_ulogic 6 }) 7 #dd easity; 8 architecture arch of distch is 8 begin 6 begin 7 process(es, d)

In the architecture we use a process that is sensitive to both inputs.

#### D Latches

HWMod WS24

```

1 entity dlatch is

2 port (

3 d : in std_ulogic;

4 en : in std_ulogic;

5 q : out std_ulogic

6 );

7 end entity;

8

9 architecture arch of dlatch is

10 begin

11 process(en, d)

```

#### —Sequential Circuit Elements in VHDL └─D Latches └─D Latches

In the process body we need a single if-condition, that checks whether the enable signal is asserted and assigns the signal d to q if that's the case. Should this condition be false, the signal value of q is not updated, meaning that it will retain its previous value. Notice that this exactly captures the behavioral specification of the D latch from the introduction.

#### **D** Latches HWMod **WS24** 1 entity dlatch is D d -Q q 2 port ( en en 3 d : in std\_ulogic; D Latches en : in std\_ulogic; 4 5 q : out std\_ulogic 6 ); 7 end entity; 8 architecture arch of dlatch is 9 **Operation Principle** 10 begin 11 process(en, d) 12 begin While en is high, q is assigned if en = '1' then 13 the value of d, otherwise q is 14 q <= d; not updated and simply holds end if; 15

its last value.

end process;

17 end architecture;

16

6

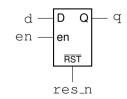

#### ─Sequential Circuit Elements in VHDL └─D Latches └─D Latch - Reset

To implement a reset mechanism for our D latch, we first extend its interface by a reset input. Naturally, we use an active-low reset.

#### D Latch - Reset

HWMod WS24

beq. Elem. Introduction D Latches Reset D Flip-Flop LFSR

1 entity dlatch\_r is

2 port (

3 res\_n : in std\_ulogic;

4 d : in std\_ulogic;

5 en : in std\_ulogic;

6 q : out std\_ulogic

7 );

8 end entity;

#### ─Sequential Circuit Elements in VHDL └─D Latches └─D Latch - Reset

In our latch process we first have to extend the sensitivity list to also include the reset input.

#### D Latch - Reset

HWMod WS24

```

1 entity dlatch_r is

2 port (

3 res_n : in std_ulogic;

d : in std_ulogic;

4

en : in std_ulogic;

5

6

q : out std_ulogic

7

);

8 end entity;

9

10 architecture arch of dlatch_r is

11 begin

12 process(en, d, res_n)

```

#### —Sequential Circuit Elements in VHDL └─D Latches └─D Latch - Reset

Then we introduce the reset condition. Since the reset signal is active-low, we need to test it for the value zero. If this condition is true, the output q is simply set to zero.

#### D Latch - Reset

HWMod WS24

```

1 entity dlatch_r is

2 port (

res_n : in std_ulogic;

3

4

d : in std_ulogic;

en : in std_ulogic;

5

6

q : out std_ulogic

7

);

8 end entity;

9

10 architecture arch of dlatch_r is

11 begin

12 process(en, d, res_n)

13 begin

14

if res_n = '0' then

q <= '0';

15

```

#### ─Sequential Circuit Elements in VHDL └─D Latches └─D Latch - Reset

The code that tests the enable signal goes in the else-if-branch. This means that the enable signal is only evaluated, if the reset is not active. Hence, the reset always overrides the internal state of the latch.

#### D Latch - Reset

HWMod WS24

```

1 entity dlatch_r is

2 port (

res_n : in std_ulogic;

3

4

d : in std_ulogic;

en : in std_ulogic;

5

q : out std_ulogic

6

7

);

8 end entity;

9

10 architecture arch of dlatch_r is

11 begin

process(en, d, res_n)

12

begin

13

if res_n = '0' then

14

15 q <= '0';

elsif en = '1' then

16

17

q <= d;

end if;

18

19 end process;

20 end architecture;

```

—Sequential Circuit Elements in VHDL └─D Latches └─D Latch - Reset

#### D Latch - Reset

HWMod WS24

Seq. Elem. Introduction D Latches Reset D Flip-Flop LFSR

#### **Operation Principle**

The reset has the highest priority. If res\_n is low the values of d and en are irrelevant.

```

1 entity dlatch_r is

2 port (

res_n : in std_ulogic;

3

4

d : in std_ulogic;

en : in std_ulogic;

5

6

q : out std_ulogic

7

);

8 end entity;

9

10 architecture arch of dlatch_r is

11 begin

process(en, d, res_n)

12

begin

13

14

if res_n = '0' then

q <= '0';

15

elsif en = '1' then

16

17

q <= d;

end if;

18

19

end process;

20 end architecture;

```

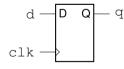

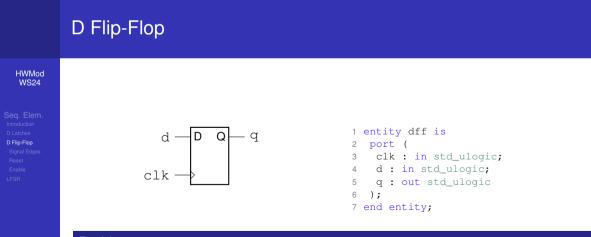

#### −Sequential Circuit Elements in VHDL └─D Flip-Flop └─**D Flip-Flop**

Let us now turn our attention to the D flip-flop. Like with the D latch, we need the input d as well as the output q. However, instead of the enable signal the D flip-flop needs a clock input to trigger its operation.

#### D Flip-Flop

#### HWMod WS24

Seq. Elem. Introduction D Latches D Flip-Flop Signal Edges Reset Enable LFSR

| 1 | entity dff is                   |

|---|---------------------------------|

| 2 | port (                          |

| 3 | <pre>clk : in std_ulogic;</pre> |

| 4 | d : in std_ulogic;              |

| 5 | q : out std_ulogic              |

| 6 | );                              |

| 7 | end entity;                     |

#### −Sequential Circuit Elements in VHDL └─D Flip-Flop └─**D Flip-Flop**

Furthermore, we need to react to signal events, that is transitions, rather than the state of a signal. This requires the introduction of a new VHDL language feature.

#### Problem

How can we detect the event of a signal transition?

#### −Sequential Circuit Elements in VHDL └─D Flip-Flop └─**D Flip-Flop**

Holperfunction Institute stateg\_edge(signal s + std\_ulogic) return boolean is begin a return (...); end function;

Let's say we have a helper function <code>rising\_edge</code> that takes a signal of type <code>std\_ulogic</code> and returns a Boolean. The function shall only return true when a rising edge has just occurred on signal S and false otherwise. On the following slides we will investigate how we can implement such a function in VHDL.

#### D Flip-Flop

#### HWMod WS24

Seq. Elem. Introduction D Latches D Flip-Flop Signal Edges Reset Enable LFSR

#### Helper function

```

1 function rising_edge(signal s : std_ulogic) return boolean is

2 begin

3 return [...];

```

4 end function;

#### —Sequential Circuit Elements in VHDL └─D Flip-Flop └─**D Flip-Flop**

Helper function

Person function

P

Using this helper function we can then implement the architecture of the D flip-flop in a quite straight-forward way. As with the D latch we first create a process. However, now, we only need the clock signal in the sensitivity list as the process only needs to be evaluated when an event happens on the clock signal. Then we use an if-condition and our helper function to check if a rising clock edge occurred. If this is the case we assign d to q. Now the only question that remains is how the body of the rising\_edge function can be implemented. In other words: What expression must be inserted instead of the place-holder in the function body?

#### D Flip-Flop HWMod **WS24** Helper function 1 function rising\_edge(signal s : std\_ulogic) return boolean is 2 begin 3 return [...]; D Flip-Flop 4 end function; D flip-flop architecture 1 architecture arch of dff is 2 begin 3 process (clk) 4 begin 5 if rising\_edge(clk) then 6 q <= d; 7 end if; 8 end process; 9 end architecture;

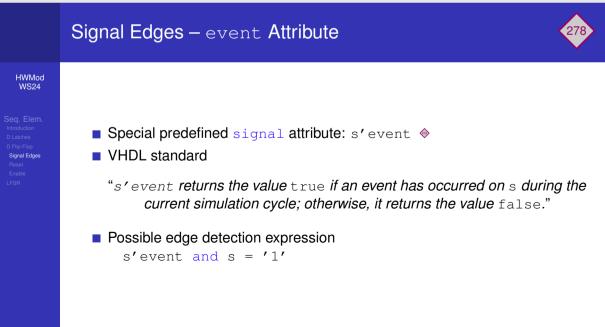

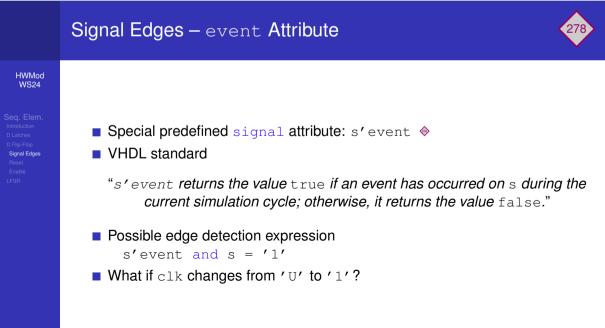

Luckily the VHDL standard defines the "event" attribute for signals which we can use for our purpose.

### Signal Edges – event Attribute

HWMod WS24

Seq. Elem. Introduction D Latches D Flip-Flop Signal Edges Reset Enable LFSR

■ Special predefined signal attribute: s'event ♦

■ Special predefined signal attribute: s'event ◆ ■ VHDL standard "s"event returns the value true # an event has occurred on s during the current studiation cycle: unterwrete, if returns the value filme."

278

As stated by the short excerpt from the VHDL standard shown on the slide, the event attribute returns the Boolean value true whenever there occurred an event during the current simulation cycle. If no event occurred, the attribute will return false.

### Signal Edges – event Attribute 278 HWMod WS24 Special predefined signal attribute: s'event \* VHDL standard s'event returns the value true if an event has occurred on s during the current simulation cycle; otherwise, it returns the value false."

Special produined signal attribute s\* event. ♦ VHOL standard "s\* event refurse the value s issue if an owen has occurred on s during the common attribution cycle otherwise, if mutures the value is list." Passale edge detection expression s\* events and s = r^1 s\*

278

We can harness this attribute to express a simple condition for detecting rising edges, as shown on the slide. This Boolean expression will evaluate to true whenever the signal s transitioned to one in the current cycle. You might want to pause the video at this point and think about whether this expression leads to undesired behavior.

—Sequential Circuit Elements in VHDL └─D Flip-Flop └─**Signal Edges – event Attribute**

Spools predefined signal attribute: s\*evens WHDL tatachard \*s\*evens than the value some share need has accounted on a during the conver samulation operation second statution operation \*s\*event second status = -12 Multiple share when the size -17 \*second status = -12 \*second s

278

As you probably detected yourself, a potential issue of this expression is that it detects arbitrary changes to the value one. For example, it will also evaluate to true when the clock signal changes from uninitialized to 1. Naturally, this does not correspond to a rising clock edge. How can we deal with this issue?

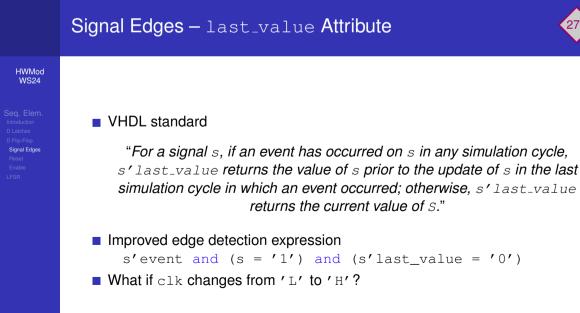

### —Sequential Circuit Elements in VHDL └─D Flip-Flop └─**Signal Edges – last\_value Attribute**

VHDL standard "For a signal ..., if an event has occurred on ... in any simulation cycle, stlasst-value returns the value of ... prior to the update of ... in the last simulation cycle in which an event occurred; otherwise, stlast\_value returns the current value of ...

279

Again, the VHDL standard comes to the rescue with an attribute. In case an event already occured on a signal s, the last\_value attribute returns the value of the signal before the most recent event.

### Signal Edges – last\_value Attribute

Seq. Elem. Introduction D Latches D Flip-Flop Signal Edges Reset Enable LFSR

### VHDL standard

"For a signal *s*, if an event has occurred on *s* in any simulation cycle, *s'last\_value* returns the value of *s* prior to the update of *s* in the last simulation cycle in which an event occurred; otherwise, *s'last\_value* returns the current value of *s*."

### —Sequential Circuit Elements in VHDL └─D Flip-Flop └─**Signal Edges – last\_value Attribute**

VHOL standard

"For a signal, i, if an event has occurred on a in any simulation cycle, a "larst-put inform the value of a prior to the update of a in the last simulation cycle in which an event occured otherwise, a "larst-put large mitram the current walle of a"."

Improved edge detection expression a "event and (a - 1") in direct (x-larst-put)er

279

We can use this attribute to refine our edge detection expression such that it only evaluates to true whenever an event occurred on the respective signal and this event led to a transition from the value zero to one. So, are we done? Is this expression valid for our purpose?

### Signal Edges – last\_value Attribute

### HWMod WS24

Seq. Elem. Introduction D Latches D Flip-Flop Signal Edges Reset Enable LFSR

### VHDL standard

"For a signal *s*, if an event has occurred on *s* in any simulation cycle, *s'last\_value* returns the value of *s* prior to the update of *s* in the last simulation cycle in which an event occurred; otherwise, *s'last\_value* returns the current value of *s*."

### Improved edge detection expression

s'event and (s = '1') and  $(s'last_value = '0')$

### —Sequential Circuit Elements in VHDL └─D Flip-Flop └─**Signal Edges – last\_value Attribute**

VEDL standard "For a gipsal.". If an event has accurated on a in any almobility cycle, where you are not any active of the transfer of the last simulation cycles, in which an event occurated. Otherwise, "L'astruvious referent the current value of 2".

Improved odge distances non-you have a standard or you have a s

279

Unfortunately not. The improved edge detection expression still comes with potential issues. Recall that our signals are in most cases actually not binary, but rather can take nine distinct values in the case of std\_ulogic. Within these nine values, the transition from zero to one is not the only valid rising edge. For example, a transition from weak low to weak high should also be detected.

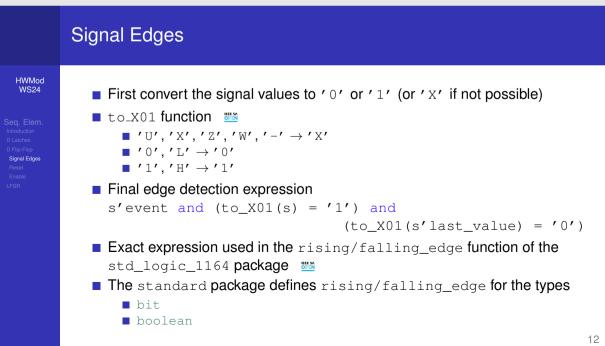

### —Sequential Circuit Elements in VHDL └─D Flip-Flop └─Signal Edges

■ First convert the signal values to ' 0' or ' 1' (or ' x' if not possible) = to\_2001 function = 0' 0' (' x' x' x' x' x' ' x' → ' x' = 0' 0' (' x' - 1' x'') = 0' (' x' - 1' x'') = 0' (' x' - 1' x'')

A simple way to handle this problem is by reducing the set of values we consider in our <code>rising\_edge</code> function by mapping the nine values to their binary equivalents if possible, and otherwise to "X". For that purpose the <code>std\_logic\_1164</code> package contains the <code>to\_X01</code> function, performing the mapping shown on the slide.

### Signal EdgesProved<br/>Notation<br/>Signal EdgesSequence<br/>Signal Edges<br/>Signal Edge

### ─Sequential Circuit Elements in VHDL └─D Flip-Flop └─Signal Edges

= Flat convert the signal values to '0' or '1' (or 'x' if not possible) = to 0.1 kindlon [0] = flat dege detaction expression = s\*events and (to\_0.01(s) = 12) and (to\_0.01(s' last\_values) = 10')

Using this function and previously introduced attributes we can now finally write down an expression to detect rising edges of a signal. This expression is simply the one from the previous slide with the current and previous signal values being mapped to '0', '1', 'X'.

## Signal Edges WMod Vs24 Sector Process Sector Sector

### ─Sequential Circuit Elements in VHDL └─D Flip-Flop └─Signal Edges

First convert the signal values to 5° or 1° (or 1° (or 1°) (or 2° or 1° (or 2° or 1° (or 2° or 1°) (or 2° or 1° (or 2° or 1°) (or 1°) (or 2° or 1°) (or 1°) (or 2° or 1°) (

This expression is the exact same one as used in the IEEE implementation and is not subject to the issues we mentioned before. For the sake of completeness, note that the IEEE also defines a similar function for detecting falling edges.

# Signal Edges FWS2 = First convert the signal values to '0' or '1' (or 'X' if not possible) = to\_X01 function = '0', 'X', 'Z', 'W', '-' → 'X' = '0', 'L' → '0' = '1', 'H' → '1' Final edge detection expression s'event and (to\_X01(s) = '1') and (to\_X01(s'last\_value) = '0') Exact expression used in the rising/falling\_edge function of the std\_logic\_1164 package

─Sequential Circuit Elements in VHDL └─D Flip-Flop └─Signal Edges

Finally, we want to mention that the rising and falling edge functions are not only defined for signals of the type std\_ulogic, but also for the bit and boolean types in the standard package.

### −Sequential Circuit Elements in VHDL └─D Flip-Flop └─**Reset**

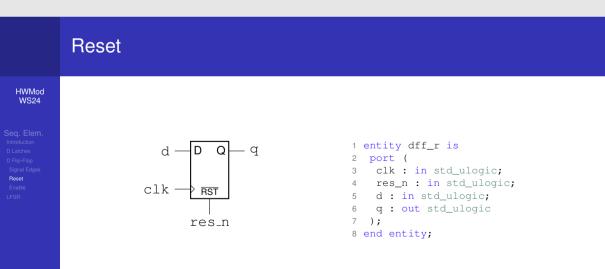

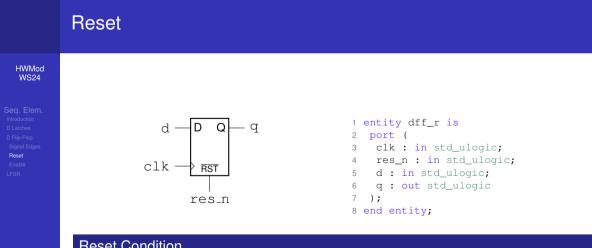

Just as for the latch, it must be possible to reset a flip-flop. Again, we use a dedicated reset input for that. The slide shows the respective symbol and entity declaration. However, whereas the semantics of the reset are rather obvious for a latch, they are less clear for a flip-flop.

### -Sequential Circuit Elements in VHDL -D Flip-Flop -Reset

| clk                          | <pre>: extity df_r is : point ( : s olk : in std_ulogin; : d rem_h : in std_ulogin; : d : im std_ulogin; : d : im std_ulogin; : q : out std_ulogin; : nod entity; : s and entity; </pre> |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset Condition              |                                                                                                                                                                                          |

| When is the reset evaluated? |                                                                                                                                                                                          |

In particular: Is the reset evaluated only at the active clock edges of the flip-flop, or is it level-sensitive and resets the flip-flop independent of the clock?

### **Reset Condition**

When is the reset evaluated?

### ─Sequential Circuit Elements in VHDL └─D Flip-Flop └─**Reset (Cont'd)**

Synchronous Reset = Reset signal is only walkated at the active dock dege = rese\_n not part of the sensitivity int = presential = for a signal part of the sensitivity = for a signal part of the sensi

The answer is that both interpretations of the reset are possible. Depending on the desired behavior, a flip-flop can in general be equipped with either reset type. A reset that is only evaluated at the active clock edge is called a synchronous reset for obvious reasons. When describing this in VHDL it is important to omit the reset from the respective sensitivity list, as we only want clock edges to trigger the process. The code snippet on the slide shows this. Also note that the reset condition check is nested within the condition for the rising clock edge.

### Reset (Cont'd) HWMod Synchronous Reset **WS24** Reset signal is only evaluated at the active clock edge res\_n not part of the sensitivity Beset list 1 process(clk) 2 begin 3 if rising\_edge(clk) then if res\_n = '0' then 4 q <= '0'; 5 6 else 7 q <= d; 8 end if; 9 end if; end process;

—Sequential Circuit Elements in VHDL └─D Flip-Flop └─**Reset (Cont'd)**

end if;

end process;

9

10

The other flavor of reset is the asynchronous one, which will reset the flip-flop whenever the reset is active, independently of the clock. In the respective VHDL code this is reflected by the reset being included in the sensitivity list. Furthermore, the condition for the reset precedes, and thus dominates, the one for the rising clock edge.

|                                                                                                                    | Reset (Cont'd)                                                                                                                                         |                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| HWMod<br>WS24<br>Seq. Elem.<br>Introduction<br>D Latches<br>D Filp-Flop<br>Signal Edges<br>Reset<br>Enable<br>LFSR | <ul> <li>Synchronous Reset</li> <li>Reset signal is only evaluated at the active clock edge</li> <li>res_n not part of the sensitivity list</li> </ul> | Asynchronous Reset <ul> <li>Reset signal is level-sensitive</li> <li>res_n part of the sensitivity list</li> </ul>                                |

|                                                                                                                    | <pre>1 process(clk) 2 begin 3 if rising_edge(clk) then 4 if res_n = '0' then 5 q &lt;= '0'; 6 else 7 q &lt;= d; 8 end if;</pre>                        | <pre>1 process(clk, res_n) 2 begin 3 if res_n = '0' then 4 q &lt;= '0'; 5 elsif rising_edge(clk) then 6 q &lt;= d; 7 end if; 8 end process;</pre> |

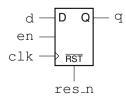

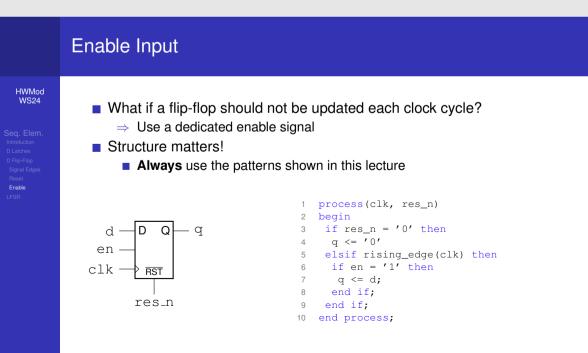

### −Sequential Circuit Elements in VHDL └─D Flip-Flop └─**Enable Input**

What if we want a flip-flop that does not update its value in each clock cycle? For example, a design might be in an overall state where certain flip-flops or registers must hold their values, although their inputs might change.

### **Enable Input**

HWMod WS24

Seq. Elem. Introduction D Latches D Flip-Flop Signal Edges Reset Enable LFSR What if a flip-flop should not be updated each clock cycle?

What if a flip-flop should not be updated each clock cycle?

### ─Sequential Circuit Elements in VHDL └─D Flip-Flop └─Enable Input

| <ul> <li>What if a flip-flop sho</li> <li>Use a dedicated e</li> </ul> | uld not be updated each clock cycle?<br>nable signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| d D q<br>clk Ref<br>res_n                                              | $\begin{array}{cccc} & promotestable, resp.c) \\ z & legis \\ z & if eq. s - 4s' then \\ d & < -5s' \\ z & dif ratio_sdip(d)(z) the \\ z & if ratio_sdip(d)(z) the \\ z & if ratio_sdip(d)(z) \\ z & odd if \\$ |

We can achieve this by using a dedicated enable input in addition to the clock, reset and data inputs. A respective flip-flop symbol and VHDL code modeling an asynchronous reset and a synchronous enable are shown on the slide. Note how the condition for the enable signal is contained within the body of the elsif branch. Thus, the enable can only take effect at rising clock edges.

### Enable Input

HWMod WS24

Seq. Elem. Introduction D Latches D Flip-Flop Signal Edges Reset Enable What if a flip-flop should not be updated each clock cycle?

⇒ Use a dedicated enable signal

```

1 process(clk, res_n)

2 begin

3

if res_n = '0' then

q <= '0'

4

5

elsif rising_edge(clk) then

if en = '1' then

6

7

q <= d;

end if;

8

9

end if;

end process;

10

```

### —Sequential Circuit Elements in VHDL └─D Flip-Flop └─Enable Input

| <ul> <li>What if a flip-flop should not be updated each clock cycle?</li> <li>Use a dedicated enable signal</li> <li>Structure matters!</li> </ul> |                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Always use the pr                                                                                                                                  | atterns shown in this lecture                                                                                                                                                                                                                                                 |  |  |  |  |  |

| d D q<br>clk Rat<br>res.n                                                                                                                          | : process(ilk, res_n)<br>: legin<br>: if $res_n = r^{-1}$ then<br>: $q < r > res_n = r^{-1}$ then<br>: $q < r > res_n = r^{-1}$ then<br>: $q < r > r > res_n = r^{-1}$ then<br>: $q < r > r > r > r > r > res = r^{-1}$ then<br>: $q < r > r > r > r > r > r > r > r > r > r$ |  |  |  |  |  |

Before we close this lecture with a simple design example, we really want to stress an important point. It is vital that you strictly stick to the code patterns for latches and flip-flops presented in this lecture. Do not experiment with custom flip-flop descriptions! It might be the case that such structures work in simulation but fail to synthesize or, even worse, result in a circuit that does not match the intended design. Synthesis tools look for the code patterns presented here and will – if you stick to them – generate correct circuits! Please always keep that in mind when writing VHDL code!

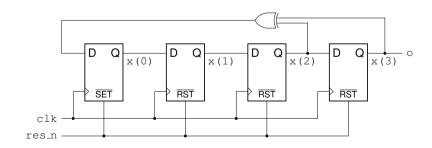

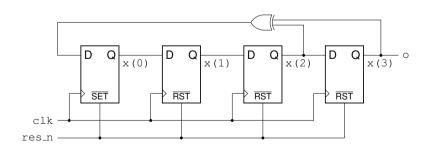

### -Sequential Circuit Elements in VHDL Linear Feedback Shift Register **Example: 4-bit LFSR**

Linez Fachack Shift Register

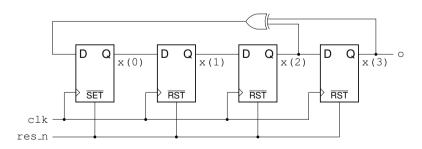

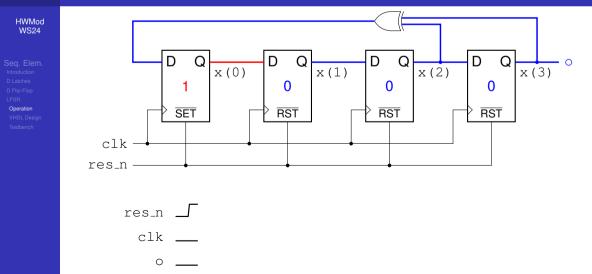

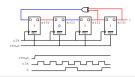

Finally, let us look at a more elaborate example design using the synchronous design style and flip-flops. The slide shows the schematic of a circuit called a linear-feedback-shift-register, abbreviated as "LFSR".

### Example: 4-bit LFSR

HWMod WS24

Linear Feedback Shift Register

### -Sequential Circuit Elements in VHDL Linear Feedback Shift Register **Example: 4-bit LFSR**

Lives Foodback Shift Register

Lives (Frequency Shift Register)

As the name suggests, such circuits revolve around a so-called shift register fed by a linear combination of its current state. A shift register is a chain of flip-flops where each flip-flop samples the output of its predecessor, thus essentially shifting the currently stored bits by one flip-flop per clock period.

### Example: 4-bit LFSR

HWMod WS24

- Linear Feedback Shift Register

- Chain of FFs (*shift-register*) fed by linear combination of its current state

### -Sequential Circuit Elements in VHDL Linear Feedback Shift Register **Example: 4-bit LFSR**

Such circuits are often used as pseudo-random number generators, which means that they can generate a sequence of bits that looks like it is random while it actually is not. We will now briefly demonstrate its operation without getting into details about the involved mathematics.

### Example: 4-bit LFSR

HWMod WS24

- Linear Feedback Shift Register

- Chain of FFs (*shift-register*) fed by linear combination of its current state

- Pseudo-random sequence of bits

### -Sequential Circuit Elements in VHDL Linear Feedback Shift Register LFSR - Circuit Operation Principle

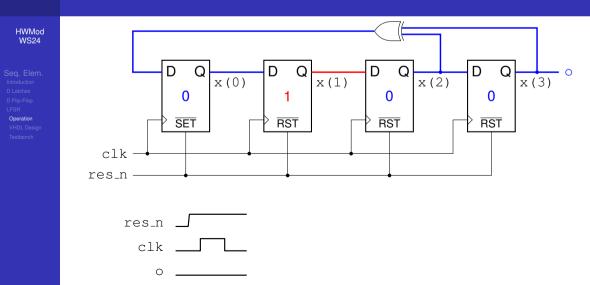

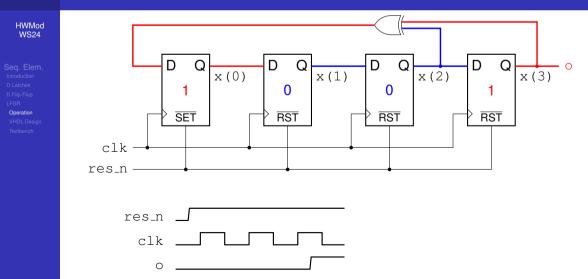

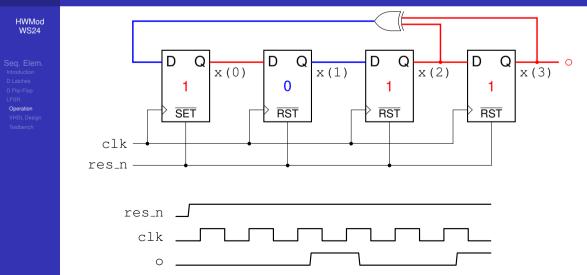

In this illustration of the "LFSR" the data wires of the circuit are highlighted in blue when propagating a logical zero, and in red for logical ones. We also show the logical value currently held by each flip-flop and a timing diagram of the inputs and outputs. As you already heard, an initial reset is paramount for every state-holding element. Therefore, this is done first leading to almost all flip-flops being set to zero. The first flip-flop, featuring an active-low set signal rather than a reset, is set to 1. This is vital, as all flip-flops being zero would result in the output being constantly zero as well. That's not very random.

### ─Sequential Circuit Elements in VHDL └─Linear Feedback Shift Register └─LFSR - Circuit Operation Principle

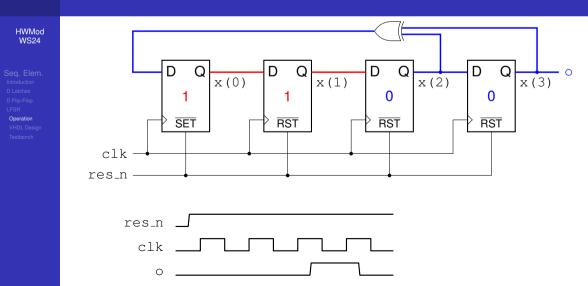

At the first rising clock edge, all flip-flops sample their inputs, leading to the stored one being shifted to the right and the left-most flip-flop to store zero now.

-Sequential Circuit Elements in VHDL Linear Feedback Shift Register LFSR - Circuit Operation Principle

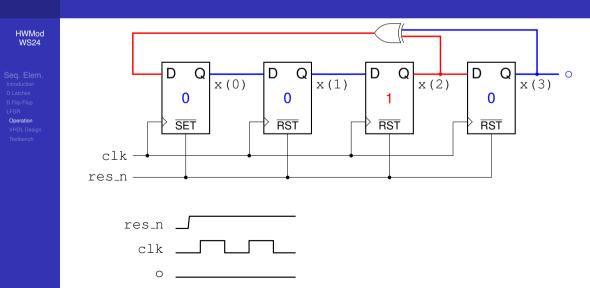

At the next clock edge, the current register bits are shifted again, making the feedback path high.

### ─Sequential Circuit Elements in VHDL └─Linear Feedback Shift Register └─LFSR - Circuit Operation Principle

The first flip-flop now sampled the one from the feedback path, while the already stored one shifted into the last flip-flop, asserting the output signal.

Sequential Circuit Elements in VHDL

Linear Feedback Shift Register

LFSR - Circuit Operation Principle

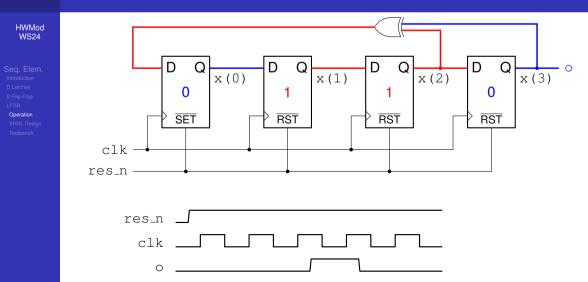

The shifting of bits continues, making the output low again.

### ─Sequential Circuit Elements in VHDL └─Linear Feedback Shift Register └─LFSR - Circuit Operation Principle

The "LFSR" continues in this fashion of sampling the feedback and shifting its internal state, producing a sequence of zeros and ones at its output.

-Sequential Circuit Elements in VHDL Linear Feedback Shift Register LFSR - Circuit Operation Principle

The shifting now leads to the output being set for two consecutive clock cycles. However, by now you have likely gotten the hang of it, and we can continue by discussing how such a circuit can be described in VHDL.

recipy life is

recipient

reci

The slide shows an entity declaration for the "LFSR" circuit. Naturally, it contains a clock, reset and output port. Let us now look at the accompanying architecture.

### LFSR - VHDL Design

### HWMod WS24

```

1 entity lfsr is

2 port (

3 clk : in std_ulogic;

4 res_n : in std_ulogic;

5 o : out std_ulogic

6 );

7 end entity;

```

The architecture declares a single vector signal for the register "x". To model this register, we create a process that asynchronously resets this signal and updates it at rising clock edges. During the reset, all bits of "x", except for the one at index zero, are reset to zero via an aggregate expression. The first bit is set to one to model the asynchronous set of the left-most flip-flop. At rising clock edges, the register is updated such that it implements the introduced "LFSR". In particular, this means that we connect the distinct bits of the register to form a chain of flip-flops, where each flip-flop samples the output of its predecessor at a rising clock edge. The left-most flip-flop samples the XOR of the bits two and three. Finally, we use a concurrent signal assignment to connect the output of the right-most flip-flop to the output port  $\circ$ .

### LFSR - VHDL Design

HWMod WS24

Ceq. Elem. Introduction D Latches D Flip-Flop LFSR Operation VHDL Design Testbanch

1 entity lfsr is

2 port (

3 clk : in std\_ulogic;

4 res\_n : in std\_ulogic;

5 o : out std\_ulogic

6 );

7 end entity;

```

1 architecture arch of lfsr is

2

signal x : std_ulogic_vector(0 to 3);

3 begin

sync : process(clk, res_n)

4

5

begin

6

if res n = '0' then

x <= (0 => '1', others => '0');

7

elsif rising_edge(clk) then

8

9

x(0) \le x(2) xor x(3);

x(1) <= x(0);

11

x(2) <= x(1);

12

x(3) <= x(2);

end if;

14

end process;

15

o <= x(3);

16 end architecture;

```

1 architecture beach of lety to 2 signal ack : add\_niosing 3 signal ack : add\_niosing 4 signal ack : add\_niosing 4 signal ack : add\_niosing 4 5 begin 4 use : excity work.lfar 10 click : add\_n 10 clic

To conclude this example, let us discuss how a testbench can be written for the "LFSR". In particular, a synchronous design like this one obviously requires a clock during simulation. But where does this clock signal come from? Well, as for all inputs of the unit-under-test, the testbench has to generate and apply it. We will now show you how this can be done.

### LFSR - Testbench

### HWMod WS24

```

1 architecture bench of lfsr tb is

2 signal clk : std_ulogic;

3

signal res_n : std_ulogic;

signal o : std ulogic;

4

5

6

7

8 begin

9

uut : entity work.lfsr

10

11

port map (

12

clk => clk,

res_n => res_n,

13

14

\circ => \circ

15

);

```

$\begin{array}{cccc} 1 & \operatorname{sech}(\operatorname{sech}(\mathcal{A})) & \operatorname{sech}(\mathcal{A}) & \operatorname{sech$

First, we declare an additional constant and signal. The constant holds the desired clock period, in this case we choose ten nanoseconds. However, in general, a design is specified to work within a range or with a particular clock frequency which should then also be generated by the testbench. The purpose of the stop\_clk signal will become clear in a moment.

### LFSR - Testbench

### HWMod WS24

```

1 architecture bench of lfsr tb is

signal clk : std_ulogic;

2

3

signal res_n : std_ulogic;

signal o : std_ulogic;

4

5

constant CLK PERIOD : time := 10 ns;

6

7

signal stop_clk : boolean := false;

8 begin

9

uut : entity work.lfsr

10

11

port map (

12

clk => clk,

res_n => res_n,

13

14

\circ => \circ

15

);

```

and processing of the procesing of the processing of the processing of the proc

However, first we create a dedicated clock generation process. This non-synthesizable code periodically toggles the clock signal. The desired clock period is achieved by waiting for half the respective constant after each assignment. If we want the simulation to terminate automatically, we must ensure that all signals become stable eventually. This includes the clock signal. Therefore, we wrap the assignments to the clock signal in a while-loop that runs until the stop\_clk signal becomes true. After that, the clock remains stable, and the clock generation process will wait indefinitely. This stop signal will be set by the stimulus process once it is done with testing the unit-under-test. We will now look at this process.

### LFSR - Testbench

### HWMod WS24

```

1 architecture bench of lfsr tb is

signal clk : std_ulogic;

2

3

signal res_n : std_ulogic;

signal o : std ulogic;

4

5

constant CLK PERIOD : time := 10 ns;

6

7

signal stop_clk : boolean := false;

8 begin

9

uut : entity work.lfsr

10

11

port map (

12

clk => clk,

13

res_n => res_n,

14

\circ => \circ

15

);

```

```

1

clkgen : process

2

begin

while not stop_clk loop

3

clk <= '0';

4

wait for 0.5*CLK_PERIOD;

5

6

clk <= '1';

7

wait for 0.5*CLK PERIOD;

8

end loop:

9

wait;

end process;

10

```

|    |                                      | 1   | clkgen : process<br>begin |

|----|--------------------------------------|-----|---------------------------|

|    |                                      | - 1 | while not stop olk loop   |

|    | architecture bench of lfar th is     | - 2 | olk <- '0'i               |

| 2  | signal olk ; and plosic;             |     | wait for 0.5+CLX PERIO    |

|    | signal yes n ; and ulogic;           |     | olk <= '1';               |

|    | signal o a std plogica               |     | wait for 0.5+CLR PERIO    |

|    |                                      |     | end loops                 |

|    | constant CLE PERIOD : Line :- 10 par |     | waite                     |

|    | signal stop olk ; boolean ;- false;  | 10  | end processy              |

|    | besio                                |     |                           |

|    |                                      | 12  | stimulus ; process        |

| 12 | unt a entity work.lfer               | 13  | begin                     |

|    | post map (                           | 14  | res p <= 1011             |

| 12 | olk -> olk.                          | 15  | wait until vising edge to |

| 12 | res n -> res n.                      | 16  | wait until vising edge to |

| 16 | 0 -> 0                               | 17  | pes p <= '1')             |

| 11 | 24                                   | 18  | wait for Secur PERSON     |

|    |                                      | 79  | stop olk <- trues         |

|    |                                      | 20  | WAITA                     |

|    |                                      | 21  | end process:              |

The first task of the stimulus process is to reset the "UUT", which is also done by the shown code. As already mentioned, otherwise the design might be in an arbitrary state which prohibits proper testing. Note that the reset should be applied for some time, ideally more than a clock cycle to ensure that everything is properly reset. In this case we set the active-low reset to low for two clock cycles. Afterwards, we let the "LFSR" run for six clock periods and then stop the clock. The simulation will then be able to automatically terminate because all signals are stable.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18 19

20

21

### LFSR - Testbench

### HWMod WS24

```

1 architecture bench of lfsr tb is

signal clk : std_ulogic;

2

3

signal res_n : std_ulogic;

signal o : std ulogic;

4

5

6

constant CLK PERIOD : time := 10 ns;

7

signal stop_clk : boolean := false;

8 begin

9

uut : entity work.lfsr

10

11

port map (

12

clk => clk,

13

res_n => res_n,

14

\circ => \circ

15

);

```

```

clkgen : process

begin

while not stop_clk loop

clk <= '0';

wait for 0.5*CLK_PERIOD;

clk <= '1';

wait for 0.5*CLK PERIOD;

end loop;

wait;

end process;

stimulus : process

begin

res n <= '0';

wait until rising_edge(clk);

wait until rising_edge(clk);

res_n <= '1';

wait for 6*CLK_PERIOD;

stop_clk <= true;</pre>

wait;

end process;

19

```

Thank you for listening! We recommend you to immediately take the self-check test in TUWEL, to see if you understood the material presented in this lecture.

### HWMod WS24

Seq. Elem. Introduction D Latches D Filp-Flop LFSR Operation VHDL Design Testbench

### Lecture Complete!

Modified: 2025-03-12, 16:32 (21636bb)