# Hardware Modeling [VU] (191.011) – WS25 –

9-Valued Logic and Resolution (IEEE 1164)

Florian Huemer & Sebastian Wiedemann & Dylan Baumann

WS 2025/26

# Motivation | Wired-AND

HWMod

WS25

IEEE 1164

Motivation

Standard

VHDL Types

Resolution

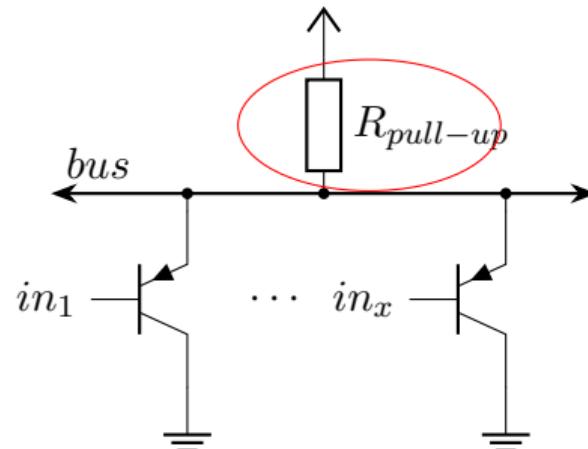

- Example: Wired-AND circuit

- A pull-up resistor pulls *bus* to HIGH when none of the transistors is active

- Setting one of the inputs  $in_1, \dots, in_x$  to LOW overrides the pull-up

- How can we model this overriding behavior?

- ⇒ We cannot model this with Boolean values alone!

# Motivation | Tri-State Buffer

HWMod

WS25

IEEE 1164

Motivation

Standard

VHDL Types

Resolution

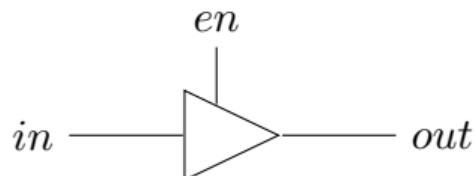

- Another example: *tri-state* buffer

- $en = 1 \Rightarrow$  buffer is *transparent*:  $in$  propagated to  $out$

- $en = 0 \Rightarrow$  buffer is *disabled*: high impedance at  $out \Rightarrow$  overriding by active driver possible

- ⇒ We cannot model this with Boolean values alone!

# The IEEE std\_logic\_1164 package

HWMOD

WS25

IEEE 1164

Motivation

Standard

Package

Value System

VHDL Types

Resolution

- Recall from *Digital Design* lecture: 9-valued logic

- Contains values for different driver strength / impedance

- Also values useful for simulation and synthesis

- ⇒ IEEE 1164 standard for VHDL

- Implemented in the std\_logic\_1164 package

- Must be imported via

```

library ieee;

use ieee.std_logic_1164.all;

```

- ⇒ Get access to two 9-valued logic (and related) types:

- *Unresolved*: std\_ulogic

- *Resolved*: std\_logic

The standard defines nine values and example use cases

| Value | Name | Example Use Case |

|-------|------|------------------|

|-------|------|------------------|

# IEEE 1164 std\_ulogic Type

HWMod

WS25

IEEE 1164

Motivation

Standard

VHDL Types

std\_ulogic

std\_logic

Resolution

- Simple enumeration type with nine values

```

type std_ulogic is ('U', 'X', '0', '1', 'Z', 'W', 'L', 'H', '-');

```

IEEE SA

OPEN

- *Unresolved*: Only supports signals with **single** driver

- Multiple drivers are detected and reported (during elaboration)

1

[...]: **error**: too many drivers for signal "x"

# IEEE 1164 std\_logic Type

HWMod

WS25

IEEE 1164

Motivation

Standard

VHDL Types

std\_ulo

ic

Resolution

- Special subtype of `std_ulo`gic

```

subtype std_logic is resolved std_ulo

```

IEEE SA

OPEN

- `std_logic` has the same nine values as `std_ulo`gic

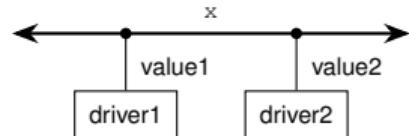

- Allows **multiple** drivers (e.g., wired-AND, tri-state bus)

- Changing the type of signal `x` in the previous example does not result in the observed error

- There are still multiple drivers  $\Rightarrow$  What value will `x` exhibit?

- Uses a *resolution function* (resolved)

# Resolution Function

HWMOD

WS25

IEEE 1164

Motivation

Standard

VHDL Types

Resolution

Overview

std\_ulogic

RES\_TABLE

- Defines resolution of multiple drivers' values into single *resolved value*

- Single parameter: Array of all values assigned to signal

- Invoked during the simulation, no real meaning for synthesis

- Resolution functions can be associated to subtypes or signals

- For subtypes: All signals of this subtype are resolved

- Arrays and records of subtypes are also supported

- For signals: Only respective signal resolved

- Example: `signal x : resolved std_ulogic;`

# The std\_ulogic Resolution Function

HWMod

WS25

IEEE 1164

Motivation

Standard

VHDL Types

Resolution

Overview

std\_ulogic

RES\_TABLE

- Resolves multiple `std_ulogic` values into a single one

# The std\_ulogic Resolution Function (cont'd)

HWMod

WS25

IEEE 1164

Motivation

Standard

VHDL Types

Resolution

Overview

std\_ulogic

RES\_TABLE

- The RES\_TABLE defines how two values are resolved into one

Example: pull-up ('H'), active ('0') and inactive ('Z') driver

```

resolve("H0Z"):

1 RES_TABLE('Z', 'H') = 'H'

2 RES_TABLE('H', '0') = '0'

3 RES_TABLE('0', 'Z') = '0'

⇒ resolve("H0Z") = '0'

```

# Lecture Complete!