# Hardware Modeling [VU] (191.011)

## – WS25 –

### VHDL Delay Mechanisms

Florian Huemer & Sebastian Wiedemann & Dylan Baumann

WS 2025/26

# Introduction

HWMod

WS25

Delay Mech.

Delay Types

Pure

Inertial

Comparison

VHDL

- Previously: `after` for delaying the assignments of signals

- Why is this needed? ⇒ Delays exist in real hardware

- Two types of delay

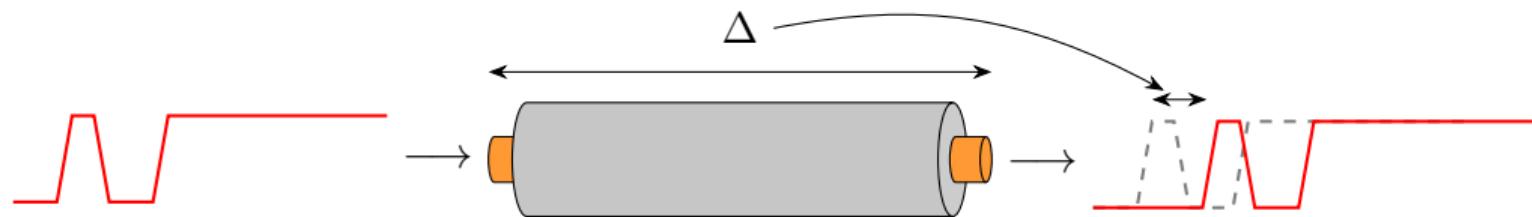

- *Pure* delay: finite signal propagation speed

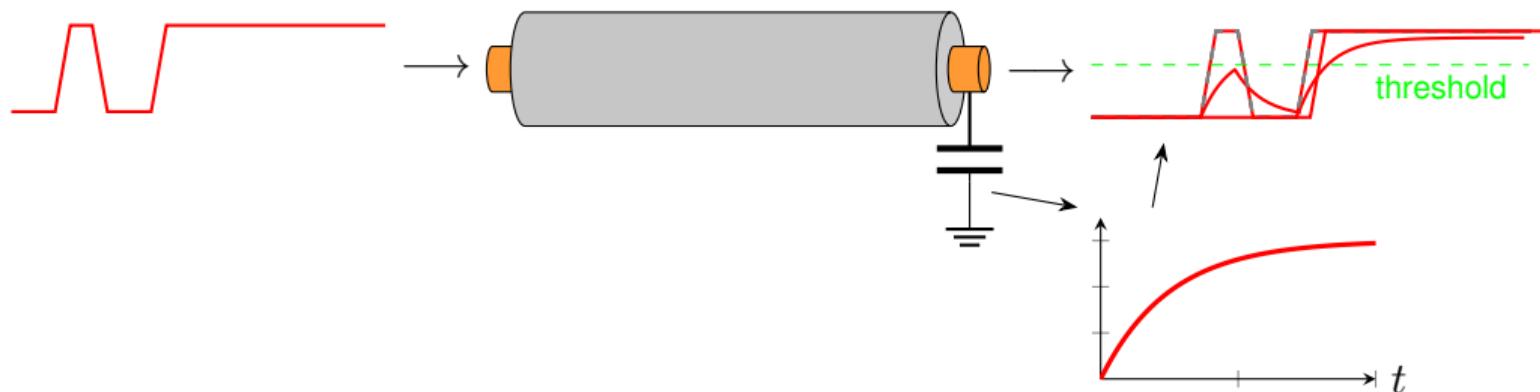

- *Inertial* delay: (dis)charging of capacitance

# Pure Delay

HWMod

WS25

Delay Mech.

Delay Types

Pure

Inertial

Comparison

VHDL

# Inertial Delay

HWMod

WS25

Delay Mech.

Delay Types

Pure

Inertial

Comparison

VHDL

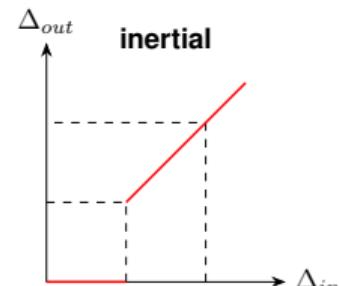

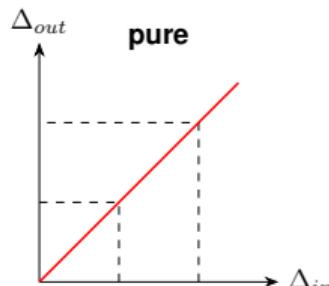

# Pure vs. Inertial Delay

HWMod

WS25

Delay Mech.

Delay Types

Pure

Inertial

Comparison

VHDL

- Pure delay

- Output wave is input wave “shifted backward” in time

- Arbitrary small pulses are propagated

- Use where capacitance negligible

- Inertial delay

- Output wave is input wave “shifted backward” in time plus pulse-width filter

- Only pulses above a certain width propagate

- Use where capacitance relevant

- Further, more specialized, models exist

- VHDL contains support for delays

```

target <= [ delay_mechanism ] waveform;

```

- Both presented delay models are supported

- Supports pure delay via `transport`

- Supports inertial delay via `reject` and `inertial`

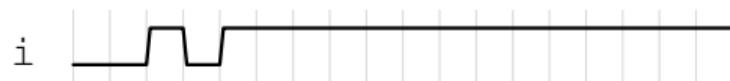

- Keyword `transport` before the waveform in an assignment

`target <= transport waveform`

- Signal assignment is simply delayed by some time

- Time given by waveform's `after` clause

- Per default 0 ns

- Example

- Default mechanism, explicit via `inertial` in an assignment

`target <= [reject time_expression] inertial waveform`

- Signal assignment is delayed and too short pulses are filtered out

- Minimum pulse width optionally defined by reject clause

- Per default time expression associated with first element of waveform

- Example

5 ns

# Remarks

HWMod

WS25

Delay Mech.

Delay Types

VHDL

Pure

Inertial

- Default is inertial delay!

- Pulse rejection time positive and smaller or equal the `after` time

- All equivalent

- `<= i after 1 ns;`

- `<= inertial i after 1 ns;`

- `<= reject 1 ns inertial i after 1 ns;`

- Any pulse shorter than the limit is rejected

- Pure delay: can convert to equivalent `inertial` delay

- `<= transport i after 10 ns;`

- `<= reject 0 ns inertial i after 10 ns;`

# Lecture Complete!