From Circuits to Code and Back

This lecture aims at giving you a more thorough understanding of how certain VHDL code structures map to hardware. We will not introduce any new language concepts and instead focus on practically applying what we already know.

C2C

Introduction

Circuit → VHDL

# Hardware Modeling [VU] (191.011) - WS24 -

From Circuits to Code and Back

Florian Huemer & Sebastian Wiedemann & Dylan Baumann

WS 2024/25

Lecture Goal

Develop an intuition for how VHDL code maps to hardware and the associated circuit complexity:

Similar to how a system-level programmer must have a good understanding of how the written program maps to the available machine instructions on a given architecture, in order to produce efficient software, you – as a hardware developer – should have a similar intuition about the mapping between VHDL code and circuits. Hence, with this lecture we want to help you to develop such an intuition, as we believe that this is a key skill in becoming a great hardware developer!

### Introduction

### Lecture Goal

Develop an intuition for how VHDL code maps to hardware and the associated circuit complexity.

From Circuits to Code and Back

Introduction

Introduction

Lecture Goal

Develop an infullion for how VHDL code maps to hardware and the associated circuit comploxity.

a Two examples

To achieve this goal we present and work through two circuit modeling examples. In the first example we take a circuit diagram and derive a VHDL entity/architecture pair that models the behavior of the given circuit. For the second example, we perform the reverse operation, taking a simple VHDL design and deriving a circuit diagram from it. We will thus effectively perform the task of the synthesis tool ourselves.

### Introduction

HWMod WS24

C2C

Introduction

Circuit  $\rightarrow$  VHDL

VHDL  $\rightarrow$  Circuit

### Lecture Goal

Develop an intuition for how VHDL code maps to hardware and the associated circuit complexity.

- Two examples

- Circuit diagram → Derive VHDL code

- VHDL code → Derive circuit diagram

-From Circuits to Code and Back -Introduction -Introduction

elop an intuition for how VHDL code maps to hardware and the associa

- Two examples

Circuit diagram → Derive VHDL code

WHDL code → Derive circuit diagram

Important VHDL concepts used in the lecture

Sequential circuit elements

Debrackens modelines

ehavioral modeling rray-types and arithmetic functions

Note that, besides other topics, this lecture heavily builds upon the videos about sequential circuit elements and behavioral modeling.

### Introduction

**HWMod**

Introduction

### Lecture Goal

Develop an intuition for how VHDL code maps to hardware and the associated circuit complexity.

- Two examples

- Circuit diagram → Derive VHDL code

- VHDL code → Derive circuit diagram

- Important VHDL concepts used in the lecture

- Sequential circuit elements

- Behavioral modeling

- Array-types and arithmetic functions

☐ From Circuits to Code and Back☐ Circuit → VHDL☐ Example 1: Circuit → VHDL Code

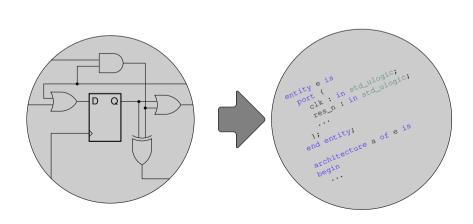

Let's start with the first example, where we take a circuit diagram and derive an appropriate VHDL design from it.

# Example 1: Circuit $\rightarrow$ VHDL Code

HWMod WS24

From Circuits to Code and Back

Circuit → VHDL

Example 1: Circuit Diagram

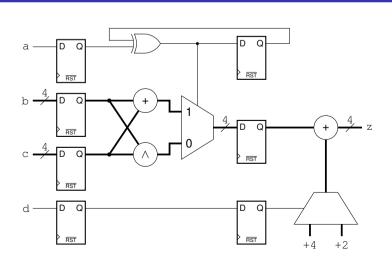

Consider the circuit shown on the slide. Before we start, note that its actual function or purpose is not important for this lecture – in fact we did not have any particular application in mind when designing this circuit. You should already know most of the used circuit symbols. The circle-shaped component with the plus sign represents an adder, while the symbol with the logical AND denotes a bit-wise AND operation. The inputs a and d are single-bit signals while d and d are four bit wide as is the single output d . Since it contains registers the circuit also has a clock and reset input. However, these signals have been omitted from the drawing, as not to clutter the figure. Thus, for the sake of completeness, imagine all registers being connected to a common clock and an active-low reset signal.

# Example 1: Circuit Diagram

HWMod WS24

```

From Circuits to Code and Back

☐ Circuit → VHDL

☐ Example 1 - Entity

```

The first step in deriving a suitable VHDL design is to derive its interface, that is, its entity declaration.

# Example 1 - Entity

```

HWMod

WS24

```

```

C2C

Introduction

Circuit → VHDL

Circuit

Entity

Architecture

Restructured

Architecture

```

```

1 entity circuit2code is

2 port (

3 clk: in std_ulogic;

4 res_n: in std_ulogic;

6 b: in std_ulogic_vector(3 downto 0);

7 c: in std_ulogic_vector(3 downto 0);

8 d: in std_ulogic;

9 z: out std_ulogic_vector(3 downto 0);

10 );

11 end entity;

```

```

From Circuits to Code and Back

Circuit → VHDL

Example 1 - Entity

```

First, we add a clock and reset input, as we will need them to implement the registers. As always, we use the <code>std\_ulogic</code> type for both of these signals. Note that the symbols used for the flip-flops in the circuit indicate an active-low reset.

# Example 1 - Entity

HWMod WS24

```

C2C

Introduction

Circuit → VHDL

Circuit

Entity

Architecture

Restructured

Architecture

```

```

1 entity circuit2code is

2  port (

3     clk : in std_ulogic;

4     res_n : in std_ulogic;

5     a : in std_ulogic;

6     b : in std_ulogic_vector(3 downto 0);

7     c : in std_ulogic_vector(3 downto 0);

8     d : in std_ulogic_vector(3 downto 0);

9     z : out std_ulogic_vector(3 downto 0)

10  );

11 end entity;

```

```

From Circuits to Code and Back

Circuit → VHDL

Example 1 - Entity

```

Next, we list all the input signals in the order of their appearance. For the signals b and c we could also have gone with the signed or the unsigned data-type. However, as the signedness of these input values does not change the way they need to be handled by the circuit, we simply settled on the  $std_ulogic_vector$  type.

# Example 1 - Entity

HWMod WS24

```

1 entity circuit2code is

2  port (

3    clk : in std_ulogic;

4   res_n : in std_ulogic;

5    a : in std_ulogic;

6    b : in std_ulogic_vector(3 downto 0);

7    c : in std_ulogic_vector(3 downto 0);

8    d : in std_ulogic_vector(3 downto 0);

9    z : out std_ulogic_vector(3 downto 0);

10  );

11 end entity;

```

```

From Circuits to Code and Back

Circuit → VHDL

Example 1 - Entity

```

Finally, we add the single, four-bit-wide, output signal z.

# Example 1 - Entity

```

HWMod

WS24

```

```

Introduction

Circuit → VHDL

Circuit

Entity

Architecture

Restructured

Architecture

```

```

1 entity circuit2code is

2 port (

3 clk: in std_ulogic;

4 res_n: in std_ulogic;

5 a: in std_ulogic;

6 b: in std_ulogic_vector(3 downto 0);

7 c: in std_ulogic_vector(3 downto 0);

8 d: in std_ulogic;

9 z: out std_ulogic_vector(3 downto 0);

10 );

11 end entity;

```

☐ From Circuits to Code and Back☐ Circuit → VHDL☐ Example 1 - Architecture

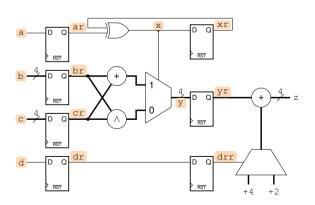

With the entity in place, we can now turn our attention to the architecture, which contains the description of the actual circuit behavior. Before we can start coding, we have to label some of the internal signals of our circuit, such that we can then refer to these signals using appropriate identifiers in the VHDL design. Let us therefore again look at the circuit.

# Example 1 - Architecture

HWMod WS24

☐ From Circuits to Code and Back☐ Circuit → VHDL☐ Example 1 - Architecture

In particular, we make sure that the inputs and outputs of all sequential elements have proper names. Therefore, for all inputs and outputs of such elements, which are not directly connected to an entity port signal, we need to introduce a proper signal name. For this example we use the following naming scheme: The output of a sequential element gets the name of its input extended by the letter  $\mathfrak{r}$ , referring to the signal being "registered". Furthermore, depending on the exact way we express the combinational parts of the circuit as VHDL code, it can also make sense to label further signals.

# Example 1 - Architecture

HWMod WS24

C2C

Introduction

Circuit → VHDL

Circuit

Entity

Architecture

Restructured

Architecture

### Circuit Preparation

Label all register inputs and outputs and other important signals!

From Circuits to Code and Back

Circuit → VHDL

Example 1 - Architecture

One candidate for such a signal is the output of the multiplexer in the lower right corner, which we simply label m.

# Example 1 - Architecture

HWMod WS24

C2C

Introduction

Circuit → VHDL

Circuit

Entity

Architecture

Restructured

Architecture

### Circuit Preparation

Label **all** register inputs and outputs and other important signals!

```

From Circuits to Code and Back

Circuit → VHDL

Architecture - Signal Declarations

```

Now we have everything we need to start implementing the architecture. We begin with the declarations for the internal signals, that we have identified and labeled in the previous step. Note that we don't declare a signal for  $\mathfrak m$  here. We will see why we don't do this shortly.

### Architecture - Signal Declarations

HWMod WS24

```

1 architecture arch of circuit2code is

2    signal br, cr, y, yr :

3        std_ulogic_vector(3 downto 0);

4    signal ar, x, xr, dr, drr : std_ulogic;

5    begin

```

```

☐ From Circuits to Code and Back☐ Circuit → VHDL☐ Architecture - Registers

```

After we declared the required internal signals, we can start to implement the behavior of our circuit within the architecture body. A good place to start are the sequential elements. Hence, we create a synchronous process by using the appropriate pattern presented in the sequential circuit elements lecture. Inside this process we write to all signals in our design that represent the output of a register. For our example these are the signals whose names end with an r.

### Architecture - Registers

#### HWMod WS24

```

6

process (clk, res_n)

begin

8

if res n = '0' then

9

ar <= '0'; dr <= '0';

10

xr <= '0'; drr <= '0';

br <= (others => '0');

11

cr <= (others => '0');

12

13

yr <= (others => '0');

elsif rising_edge(clk) then

14

15

ar <= a;

16

br \le b;

17

cr <= c;

18

dr \ll d;

19

xr <= x;

yr <= y;

20

drr <= dr;

21

22

end if;

23

end process;

```

```

└─From Circuits to Code and Back

└─Circuit → VHDL

└─Architecture - Registers

```

As always in our course, we use an asynchronous reset. Furthermore, as already noted, the circuit diagram indicates that the reset is active-low. In addition to that, because the flip-flops in the circuit feature a reset rather than a set input, we initialize all of them to zero.

# Architecture - Registers

#### HWMod WS24

```

6

process (clk, res_n)

begin

8

if res n = '0' then

ar <= '0'; dr <= '0';

9

10

xr <= '0'; drr <= '0';

11

br <= (others => '0');

cr <= (others => '0');

12

13

yr <= (others => '0');

elsif rising_edge(clk) then

14

15

ar <= a;

16

br \le b;

17

cr <= c;

dr <= d;

18

19

xr <= x;

20

yr <= y;

drr <= dr;

21

22

end if;

23

end process;

```

```

└─From Circuits to Code and Back

└─Circuit → VHDL

└─Architecture - Registers

```

On rising clock edges we simply assign each input signal of a sequential element to the appropriate output signal. For example, the signal a is assigned to ar. This process is a quite straight forward step that doesn't demand much thought and is more or less independent of the actual circuit.

# Architecture - Registers

HWMod WS24

```

6

process (clk, res_n)

begin

8

if res n = '0' then

9

ar <= '0'; dr <= '0';

10

xr <= '0'; drr <= '0';

11

br <= (others => '0');

cr <= (others => '0');

12

13

yr <= (others => '0');

elsif rising_edge(clk) then

14

15

ar <= a;

16

br \le b;

17

cr <= c;

18

dr <= d;

19

xr <= x;

vr <= v;

20

21

drr <= dr;

22

end if;

23

end process;

```

```

From Circuits to Code and Back

Circuit → VHDL

Architecture - Combinational Logic I

```

With the sequential circuit elements in place, we can now add the combinational logic between them that defines most of our circuits specific behavior.

# Architecture - Combinational Logic I

#### HWMod WS24

```

a \frac{1}{1} \frac{

```

```

x <= ar xor xr;

26

process (all)

27

begin

if x = '1' then

28

29

y <= std_ulogic_vector(

unsigned(br) +

30

unsigned(cr)

31

);

33

else

y <= br and cr;

end if:

35

end process;

```

```

From Circuits to Code and Back

Circuit → VHDL

Architecture - Combinational Logic I

```

Let's start with the XOR gate in the upper part of the circuit that produces the x signal. While there exist multiple ways to describe this logic, we can very easily express such simple gates using concurrent signal assignments. An assignment like the one highlighted on the slide typically directly maps to a single gate of the respective type for single bit signals, and to multiple such gates for multi-bit signals.

# Architecture - Combinational Logic I

#### HWMod WS24

```

a \frac{1}{1} \frac{

```

```

x <= ar xor xr;

process (all)

begin

if x = '1' then

y <= std_ulogic_vector(

unsigned(br) +

unsigned(cr)

);

else

y <= br and cr;

end if;

end process;</pre>

```

# From Circuits to Code and Back Circuit → VHDL Architecture - Combinational Logic I

For the logic that decides whether to forward the "bitwise-AND" or the sum of the signals p and p to the signal p we use a separate process. As you already know, multiplexers can be expressed using if-else statements. Hence, we test the signal p and either assign the result of the "bitwise-AND" or the addition to p. Of course this is not the only possibility how we can describe this sub-circuit in VHDL. One alternative would be to use a concurrent signal assignment with an appropriate when/else expression. However, operations comprising multiple circuit elements quickly become quite confusing using such assignments, and we therefore usually recommend the use of a process in such cases. Please note that, we would get the exact same circuit, if we would put the concurrent signal assignment for p into the process for p.

# Architecture - Combinational Logic I

#### HWMod WS24

```

a D Q ar Xr D Q Xr D Q

```

```

x <= ar xor xr;

process (all)

begin

if x = '1' then

y <= std_ulogic_vector(

unsigned(br) +

unsigned(cr)

);

else

y <= br and cr;

end if;

end process;</pre>

```

```

-From Circuits to Code and Back

-Circuit → VHDL

Architecture - Combinational Logic II

```

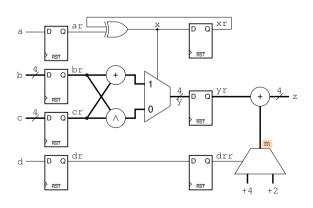

The last thing we need to do is to implement the logic that produces the output signal z. For that we use a separate process, although this is not strictly required. It would be semantically equivalent to simply add this code to the other combinational process that produces the y signal. However, it is often preferable to restrict processes to related parts of a circuit in order to give your code more structure and to improve its readability and maintainability.

41

47 48

### Architecture - Combinational Logic II

**HWMod WS24**

```

process (all)

37

38

variable m : integer:

39

begin

if drr = '1' then

40

m := 2:

m := 4:

43

44

end if;

45

z <= std_ulogic_vector(</pre>

46

unsigned(yr) + m

);

end process;

50 end architecture;

```

```

-From Circuits to Code and Back

-Circuit → VHDL

Architecture - Combinational Logic II

```

We start with the declaration of the intermediate m as a variable in the process. Since the output of the second multiplexer is only required within this process, it makes sense to restrict its scope in order to reduce needless cluttering of the architecture's name space. We select the integer data type for m. However, std ulogic vector, or unsigned would also be valid options.

> 37 38

> 39

40 41

43 44

45

46

47

48

### Architecture - Combinational Logic II

**HWMod WS24**

Architecture

```

process (all)

variable m : integer;

begin

if drr = '1' then

m := 2;

m := 4:

end if;

z <= std_ulogic_vector(</pre>

unsigned(yr) + m

);

end process;

50 end architecture;

```

```

From Circuits to Code and Back

Circuit → VHDL

Architecture - Combinational Logic II

```

Next we implement the multiplexer that selects between the constants two and four based on the value of drr and writes to the variable m.

## Architecture - Combinational Logic II

HWMod WS24

```

a D Q ar Xr D Q Xr D Q

```

```

process (all)

37

38

variable m : integer;

39

begin

if drr = '1' then

41

m := 2;

43

m := 4;

44

end if;

45

z <= std_ulogic_vector(</pre>

46

unsigned(yr) + m

47

48

);

end process;

50 end architecture;

```

```

From Circuits to Code and Back

Circuit → VHDL

Architecture - Combinational Logic II

```

Finally, we produce the output z by adding yr to m. This completes our architecture and thus also our VHDL design.

## Architecture - Combinational Logic II

HWMod WS24

```

process (all)

37

38

variable m : integer;

begin

39

if drr = '1' then

41

m := 2;

m := 4;

43

44

end if;

z <= std_ulogic_vector(</pre>

46

47

unsigned(yr) + m

48

end process;

50 end architecture;

```

```

—From Circuits to Code and Back

└─Circuit → VHDL

└─Restructured Architecture

```

Before we continue with the next example, we want to show you that there usually exist multiple different VHDL descriptions of the exact same circuit. Therefore, let us quickly discuss some example modifications to our previous VHDL code that do not change the resulting circuit. The reason why we discuss that, is to really show you the different ways to describe the exact same circuit.

```

HWMod

WS24

```

```

C2C

Introduction

Circuit → VHDL

Circuit

Entity

Architecture

Restructured

Architecture

```

```

process (clk, res_n)

1

2

begin

if res_n = '0' then

3

19

x <= ar xor xr;

ar <= '0'; dr <= '0';

4

20

xr <= '0'; drr <= '0';

5

21

process (all)

br <= (others => '0');

6

begin

22

7

cr <= (others => '0');

if x = '1' then

23

yr <= (others => '0');

8

y <= std_ulogic_vector(

9

elsif rising_edge(clk) then

unsigned(br) +

25

ar <= a;

26

unsigned(cr)

br <= b;

27

);

12

cr <= c;

28

else

dr <= d;

13

y <= br and cr;

29

xr <= x;

14

30

end if:

yr <= y;

15

end process;

drr <= dr;

16

end if;

end process;

```

# —From Circuits to Code and Back └─Circuit → VHDL └─Restructured Architecture

One thing we could do is merge the concurrent signal assignment and the process that produces the y signal into the synchronous process. This change would reduce the overall length of our architecture. However, it arguably also makes the VHDL code less structured, as we no longer have dedicated processes for synchronous and combinational parts of the circuit.

### **Restructured Architecture**

```

HWMod

WS24

```

```

process (clk, res_n)

1

2

begin

if res_n = '0' then

3

19

x <= ar xor xr;

ar <= '0'; dr <= '0';

4

20

xr <= '0'; drr <= '0';

5

21

process (all)

br <= (others => '0');

6

22

begin

7

cr <= (others => '0');

if x = '1' then

23

yr <= (others => '0');

8

y <= std_ulogic_vector(

9

elsif rising_edge(clk) then

25

unsigned(br) +

ar <= a;

26

unsigned(cr)

br <= b;

27

);

12

cr <= c;

28

else

dr \ll d;

13

29

y <= br and cr;

xr <= x;

14

30

end if;

yr <= y;

15

end process;

drr <= dr;

16

end if;

end process;

```

# From Circuits to Code and Back ☐ Circuit → VHDL ☐ Restructured Architecture

Let's start with the process. The goal is to take the shown sequence of code and replace the assignment in the synchronous process with it. However, care must be taken because the combinational process writes to the signal y, while the synchronous process writes to yr. To get semantically equivalent code, we therefore need to replace all occurrences of y by yr in the part we take from the combinational process.

```

HWMod

WS24

```

```

C2C

Introduction

Circuit → VHDL

Circuit

Entity

Architecture

Restructured

Architecture

```

```

process (clk, res_n)

1

2

begin

if res_n = '0' then

3

19

x <= ar xor xr;

ar <= '0'; dr <= '0';

4

20

xr <= '0'; drr <= '0';

5

process (all)

21

br <= (others => '0');

6

22

7

cr <= (others => '0');

if x = '1' then

23

yr <= (others => '0');

8

y <= std_ulogic_vector(

9

elsif rising_edge(clk) then

25

unsigned(br) +

ar <= a;

26

unsigned(cr)

br \le b;

);

12

cr <= c;

28

else

dr \ll d;

13

29

y <= br and cr;

xr \le x;

14

30

end if;

yr <= y; ←

15

31

end process;

16

drr <= dr;

end if;

end process;

```

```

From Circuits to Code and Back

Circuit → VHDL

Restructured Architecture

```

This slide shows the result of this modification.

```

HWMod

WS24

```

```

C2C

Introduction

Circuit → VHDL

Circuit

Entity

Architecture

Restructured

Architecture

VHDL → Circuit

```

```

if x = '1' then

1

process (clk, res_n)

15

2

begin

16

yr <= std_ulogic_vector(</pre>

unsigned(br) +

3

if res_n = '1' then

17

ar <= '0'; xr <= '0';

unsigned(cr)

4

18

dr <= '0'; drr <= '0';

5

19

);

br <= (others => '0');

20

else

7

cr <= (others => '0');

21

yr <= br and cr;</pre>

yr <= (others => '0');

8

22

end if;

elsif rising_edge(clk) then

9

23

ar <= a;

24

drr <= dr;

10

br <= b;

25

end if;

11

end process;

12

cr <= c;

26

dr <= d;

13

27

14

xr <= x;

28

x <= ar xor xr;

```

```

☐ From Circuits to Code and Back☐ Circuit → VHDL☐ Restructured Architecture

```

Notice that the synchronous process only writes to the signal yr and that the signal y is no longer needed at all. We can therefore remove its declaration altogether.

```

HWMod

WS24

```

```

C2C

Introduction

Circuit → VHDL

Circuit

Entity

Architecture

Restructured

Architecture

```

```

if x = '1' then

1

process (clk, res_n)

15

2

begin

16

yr <= std_ulogic_vector(</pre>

3

if res_n = '1' then

17

unsigned(br) +

ar <= '0'; xr <= '0';

unsigned(cr)

18

dr <= '0'; drr <= '0';

5

19

);

br <= (others => '0');

20

else

7

cr <= (others => '0');

21

vr <= br and cr;</pre>

yr <= (others => '0');

22

end if;

8

9

elsif rising_edge(clk) then

23

24

drr <= dr;

10

ar <= a;

br <= b;

25

end if:

11

12

cr <= c;

26

end process;

dr <= d;

13

27

14

xr <= x;

28

x <= ar xor xr;

```

### —From Circuits to Code and Back └─Circuit → VHDL └─Restructured Architecture

Finally, we can also remove the signal x from our design, by directly calculating the XOR function in the synchronous process as well.

```

HWMod

WS24

```

```

C2C

Introduction

Circuit → VHDL

Circuit

Entity

Architecture

Restructured

Architecture

```

```

if x = '1' then

1

process (clk, res_n)

15

yf <= std_ulogic_vector(

2

begin

16

3

if res_n = '1' then

17

unsigned(br) +

ar <= '0'; xr <= '0';

unsigned(cr)

18

dr <= '0'; drr <= '0';

5

19

);

br <= (others => '0');

20

else

7

cr <= (others => '0');

21

yr <= br and cr;

yr <= (others => '0');

8

22

end if;

9

elsif rising_edge(clk) then

23

ar <= a;

24

drr <= dr;

10

br <= b;

25

end if:

11

end process;

12

cr <= c;

26

dr <= d;

27

13

14

xr <= x*

x \leftarrow ar xor xr;

```

# From Circuits to Code and Back Circuit → VHDL Restructured Architecture

Here, we see the complete final resulting statement part of our architecture.

### Restructured Architecture

```

C2C

Introduction

Circuit → VHDL

Circuit

Entity

Architecture

Restructured

Architecture

VHDL → Circuit

```

HWMod WS24

```

1

process (clk, res_n)

else

2

begin

21

vr <= br and cr;

if res_n = '1' then

end if;

3

ar <= '0'; xr <= '0';

4

23

dr <= '0'; drr <= '0';

5

24

drr <= dr;

br <= (others => '0');

end if;

25

7

cr <= (others => '0');

26

end process;

vr <= (others => '0');

27

9

elsif rising_edge(clk) then

28

process (all)

ar <= a;

29

variable m : integer;

br <= b;

30

begin

if drr = '1' then

cr <= c;

31

12

dr <= d;

m := 2;

13

32

xr <= ar xor xr;

14

33

else

if (ar xor xr) = '1' then

34

m := 4;

15

yr <= std_ulogic_vector(</pre>

16

35

end if;

unsigned(br) +

z <= std_ulogic_vector(

17

36

unsigned(cr)

37

unsigned(yr) + m);

18

19

);

end process;

```

# From Circuits to Code and Back ☐ Circuit → VHDL ☐ Restructured Architecture

Please note that it is NOT possible to also move the last remaining combinational process generating z into the synchronous process as well. This is because the output z is not directly provided by a register, but generated combinationally out of the signals yr and drr.

### **Restructured Architecture**

```

C2C

Introduction

Circuit → VHDL

Circuit

Entity

Architecture

Restructured

Architecture

```

HWMod WS24

```

1

process (clk, res_n)

20

else

2

begin

21

vr <= br and cr;

if res_n = '1' then

3

end if;

ar <= '0'; xr <= '0';

4

23

dr <= '0'; drr <= '0';

5

24

drr <= dr;

br <= (others => '0');

end if:

25

7

cr <= (others => '0');

26

end process;

yr <= (others => '0');

27

9

elsif rising_edge(clk) then

28

process (all)

variable m : integer;

ar <= a;

29

br \le b;

30

begin

if drr = '1' then

12

cr <= c;

31

dr <= d;

13

m := 2;

14

xr <= ar xor xr;

33

else

if (ar xor xr) = '1' then

m := 4;

15

34

16

yr <= std_ulogic_vector(</pre>

35

end if;

unsigned(br) +

17

36

z <= std_ulogic_vector(

unsigned(cr)

unsigned(yr) + m);

18

37

19

);

end process;

```

From Circuits to Code and Back

VHDL → Circuit

Example 2: VHDL Code → Circuit

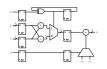

Let us now move to the second example, where we take a VHDL design and derive a circuit diagram from it.

# Example 2: VHDL Code $\rightarrow$ Circuit

HWMod WS24

```

From Circuits to Code and Back

VHDL → Circuit

Example 2: Entity

```

```

| setting medical result is

| Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image |

| Image | Image | Image | Image | Image |

| Image | Image | Image | Image | Image |

| Image | Image | Image | Image | Image | Image |

| Image |

| Image |

| Image | Im

```

This slide shows the entity declaration of our example circuit. As with the previous example the design does not serve any particular purpose, other than being an example.

# Example 2: Entity

```

HWMod

WS24

```

```

1 entity code2circuit is

generic (

N, M : positive

3

);

port (

5

clk : in std_ulogic;

6

7

res_n : in std_ulogic;

a : in std_ulogic;

8

b : in std_ulogic_vector(N-1 downto 0);

9

c : in std_ulogic_vector(M-1 downto 0);

10

d : in std_ulogic_vector(M-1 downto 0);

11

x : out std_ulogic;

12

y : out std_ulogic_vector(M-1 downto 0)

13

14

);

15 end entity;

```

```

☐ From Circuits to Code and Back☐ VHDL → Circuit☐ Example 2: Entity

```

The entity has two generics M and M that define the widths of the inputs M, M as well as of the output M.

# Example 2: Entity

```

HWMod

WS24

```

```

1 entity code2circuit is

generic (

N, M: positive

3

);

port (

5

clk : in std_ulogic;

6

res_n : in std_ulogic;

7

a : in std_ulogic;

8

b : in std_ulogic_vector(N-1 downto 0);

9

c : in std_ulogic_vector(M-1 downto 0);

10

d : in std_ulogic_vector(M-1 downto 0);

11

x : out std_ulogic;

12

y : out std_ulogic_vector(M-1 downto 0)

13

14

);

15 end entity;

```

```

From Circuits to Code and Back

VHDL → Circuit

Example 2: Entity

```

It also has a clock and reset input, indicating that it contains some sequential circuit elements.

# Example 2: Entity

```

HWMod

WS24

```

```

1 entity code2circuit is

generic (

N, M : positive

3

);

port (

5

clk : in std_ulogic;

6

res_n : in std_ulogic;

7

a : in std_ulogic;

8

9

b : in std_ulogic_vector(N-1 downto 0);

c : in std_ulogic_vector(M-1 downto 0);

10

d : in std_ulogic_vector(M-1 downto 0);

11

x : out std_ulogic;

12

y : out std_ulogic_vector(M-1 downto 0)

13

);

14

15 end entity;

```

```

☐ From Circuits to Code and Back☐ VHDL → Circuit☐ Example 2: Entity

```

Finally, the entity has an input a and an output x, both being single-bit signals.

## Example 2: Entity

HWMod WS24

```

1 entity code2circuit is

generic (

N, M : positive

3

);

port (

5

clk : in std_ulogic;

6

7

res_n : in std_ulogic;

a : in std_ulogic;

8

9

b : in std_ulogic_vector(N-1 downto 0);

c : in std_ulogic_vector(M-1 downto 0);

10

d : in std_ulogic_vector(M-1 downto 0);

11

x : out std_ulogic;

12

y : out std_ulogic_vector(M-1 downto 0)

13

);

14

15 end entity;

```

Let us now look at a given architecture for this entity. We can see that it consists of two processes.

#### Example 2: Architecture

```

HWMod

WS24

```

```

1 architecture arch of code2circuit is

process(all)

19

signal r0, r1 : std ulogic;

20

variable temp : std_ulogic;

signal r2 : c'subtype;

3

21

begin

4 begin

22

temp := '0';

process (clk, res_n)

23

for i in b'range loop

begin

temp := temp or b(i);

6

if res n = '0' then

7

end loop;

r0 <= '0'; r1 <= '0'; x <= '0';

8

9

r2 <= (others => '0');

27

y \ll r2;

elsif rising_edge(clk) then

28

r0 <= a xor r1;

29

if temp and r0 then

r1 <= r0;

30

y <= std_ulogic_vector(

12

x \leq r1;

31

to_unsigned(3, y'length)

13

r2 <= std_ulogic_vector(

32

);

14

signed(c) + signed(d)

end if:

15

33

end process;

16

);

34

end if;

17

35

end process;

36 end architecture;

```

The process on the left describes sequential circuit elements, as indicated by the usual code pattern for D flip-flops.

#### Example 2: Architecture

```

HWMod

WS24

```

```

1 architecture arch of code2circuit is

process(all)

19

signal r0, r1 : std ulogic;

20

variable temp : std_ulogic;

signal r2 : c'subtype;

begin

3

21

4 begin

22

temp := '0';

5

process (clk, res_n)

23

for i in b'range loop

begin

temp := temp or b(i);

6

7

if res n = '0' then

25

end loop;

r0 <= '0'; r1 <= '0'; x <= '0';

8

9

r2 <= (others => '0');

27

y \ll r2;

elsif rising_edge(clk) then

28

r0 <= a xor r1:

29

if temp and r0 then

r1 <= r0;

30

y <= std_ulogic_vector(

12

x \ll r1;

31

to_unsigned(3, y'length)

13

r2 <= std_ulogic_vector(

32

);

14

signed(c) + signed(d)

end if:

15

33

end process;

16

);

34

end if;

17

35

36 end architecture;

end process;

```

```

From Circuits to Code and Back

VHDL → Circuit

Example 2: Architecture

```

The other one only contains combinational logic, as is also suggested by the by now familiar all keyword in its sensitivity list. You should be familiar with all VHDL features used in this design.

#### Example 2: Architecture

HWMod WS24

```

1 architecture arch of code2circuit is

process(all)

19

signal r0, r1 : std ulogic;

20

variable temp : std_ulogic;

signal r2 : c'subtype;

3

21

begin

4 begin

temp := '0';

22

process (clk, res_n)

23

for i in b'range loop

begin

temp := temp or b(i);

6

if res n = '0' then

7

end loop;

r0 <= '0'; r1 <= '0'; x <= '0';

8

9

r2 <= (others => '0');

27

v \ll r2:

elsif rising_edge(clk) then

28

r0 <= a xor r1;

29

if temp and r0 then

r1 <= r0;

30

y <= std_ulogic_vector(

12

x \ll r1;

31

to_unsigned(3, y'length)

13

r2 <= std_ulogic_vector(

32

);

14

signed(c) + signed(d)

end if;

15

33

16

);

34

end process;

end if;

35

end process;

36 end architecture;

```

# From Circuits to Code and Back VHDL → Circuit Example 2: Architecture

The only really noteworthy thing is the declaration of the r2 signal. Here the subtype attribute is used on the input c to extract its fully-constrained type information. This is a neat way to declare a signal, variable or constant with the same type as an already declared object and saves us from re-specifying the whole type information. Unfortunately this construct is not supported by all synthesis tools, but works fine in simulation. We still wanted to include it, such that you have seen this feature once.

#### Example 2: Architecture

```

HWMod

WS24

```

```

1 architecture arch of code2circuit is

19

process(all)

signal r0, r1 : std ulogic;

variable temp : std ulogic;

20

signal r2 : c'subtype;

21

begin

temp := '0';

22

5

process (clk, res_n)

23

for i in b'range loop

begin

temp := temp or b(i);

6

7

if res n = '0' then

end loop;

r0 <= '0'; r1 <= '0'; x <= '0';

8

9

r2 <= (others => '0');

27

v <= r2;

elsif rising edge(clk) then

28

r0 <= a xor r1;

if temp and r0 then

29

r1 <= r0;

y <= std_ulogic_vector(

12

30

x \ll r1;

to_unsigned(3, y'length)

13

31

r2 <= std_ulogic_vector(

14

32

);

signed(c) + signed(d)

end if:

15

33

16

);

end process;

34

end if:

35

36 end architecture;

end process;

```

```

From Circuits to Code and Back

VHDL → Circuit

Example 2: Architecture

```

Pause the video at this point and think about how the circuit can look like. You can also make a quick paper sketch.

#### Example 2: Architecture

```

HWMod

WS24

```

```

1 architecture arch of code2circuit is

process(all)

19

signal r0, r1 : std ulogic;

20

variable temp : std_ulogic;

signal r2 : c'subtype;

3

21

begin

4 begin

22

temp := '0';

process (clk, res_n)

23

for i in b'range loop

begin

temp := temp or b(i);

6

if res n = '0' then

7

end loop;

r0 <= '0'; r1 <= '0'; x <= '0';

8

9

r2 <= (others => '0');

27

y \ll r2;

elsif rising_edge(clk) then

28

r0 <= a xor r1;

29

if temp and r0 then

r1 <= r0;

30

y <= std_ulogic_vector(

12

x \leq r1;

31

to_unsigned(3, y'length)

13

r2 <= std_ulogic_vector(

32

);

14

signed(c) + signed(d)

end if:

15

33

end process;

16

);

34

end if;

17

35

end process;

36 end architecture;

```

```

From Circuits to Code and Back

VHDL → Circuit

Example 2: Circuit - Registers

```

```

substitutions and of modesticuti is considered by the modesticution of the modesticution of

```

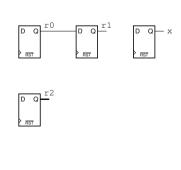

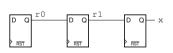

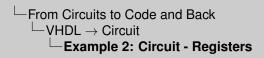

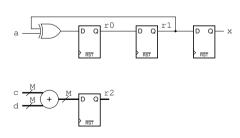

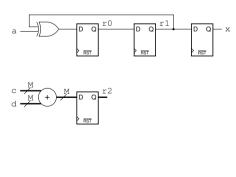

Recall that when going from a circuit diagram to VHDL code, we started by implementing the sequential circuit elements. This is also our starting point for deriving a circuit from VHDL code.

#### Example 2: Circuit - Registers

```

HWMod

WS24

```

```

1 architecture arch of code2circuit is

signal r0, r1 : std_ulogic;

signal r2 : c'subtype;

4 begin

5 process (clk, res_n)

6 begin

if res_n = '0' then

r0 <= '0'; r1 <= '0'; x <= '0';

8

r2 <= (others => '0');

9

10

elsif rising_edge(clk) then

11

r0 <= a xor r1;

r1 <= r0;

12

x \ll r1;

13

r2 <= std_ulogic_vector(

signed(c) + signed(d)

15

);

16

17

end if;

end process;

18

```

```

From Circuits to Code and Back

VHDL → Circuit

Example 2: Circuit - Registers

```

Hence, we first identify all processes that describe sequential circuit elements. As already mentioned, in our example there is only one such process.

#### Example 2: Circuit - Registers

```

HWMod

WS24

```

```

1 architecture arch of code2circuit is

signal r0, r1 : std_ulogic;

signal r2 : c'subtype;

4 begin

process (clk, res_n)

begin

6

if res_n = '0' then

r0 <= '0'; r1 <= '0'; x <= '0';

8

r2 <= (others => '0');

9

10

elsif rising_edge(clk) then

11

r0 <= a xor r1;

r1 <= r0;

12

x \ll r1;

13

r2 <= std_ulogic_vector(

signed(c) + signed(d)

15

);

16

17

end if;

18

end process;

```

```

From Circuits to Code and Back

VHDL → Circuit

Example 2: Circuit - Registers

```

Looking at this process we first identify all the signals the process writes to, as these signals represent the outputs of flip-flops. We add registers with these signals as their outputs to our circuit diagram. If you perform such a conversion on a piece of paper, be sure to leave enough space between the elements, such that you can add in the combinational logic in the next step.

#### Example 2: Circuit - Registers

```

HWMod

WS24

```

```

1 architecture arch of code2circuit is

signal r0, r1 : std_ulogic;

signal r2 : c'subtype;

4 begin

process (clk, res_n)

6

begin

if res_n = '0' then

7

r0 <= '0'; r1 <= '0'; x <= '0';

8

r2 <= (others => '0');

9

10

elsif rising_edge(clk) then

r0 <= a xor r1;

11

r1 <= r0;

12

x \ll r1;

13

14

r2 <= std_ulogic_vector(

signed(c) + signed(d)

15

16

);

end if;

17

18

end process;

```

```

From Circuits to Code and Back

VHDL → Circuit

Example 2: Circuit - Registers

```

The reset code shows that the reset is active-low and that everything must be initialized to zero. As with the other example we don't draw the clock nor the reset signal, as not to clutter the figure with to many connections. With the flip-flops in place, we can now connect their inputs to the appropriate sources.

#### Example 2: Circuit - Registers

```

HWMod

WS24

```

```

1 architecture arch of code2circuit is

signal r0, r1 : std_ulogic;

signal r2 : c'subtype;

4 begin

process (clk, res_n)

begin

6

if res_n = '0' then

7

r0 <= '0'; r1 <= '0'; x <= '0';

8

r2 <= (others => '0');

9

10

elsif rising_edge(clk) then

r0 <= a xor r1;

11

r1 <= r0;

12

x \ll r1;

13

14

r2 <= std_ulogic_vector(

signed(c) + signed(d)

15

);

16

end if;

17

end process;

18

```

```

From Circuits to Code and Back

VHDL → Circuit

Example 2: Circuit - Registers

```

Let's start with r1. The respective assignment in the synchronous process specifies that this signal gets assigned the value of r0.

#### Example 2: Circuit - Registers

```

HWMod

WS24

```

```

1 architecture arch of code2circuit is

signal r0, r1 : std_ulogic;

signal r2 : c'subtype;

4 begin

process (clk, res_n)

begin

6

if res_n = '0' then

r0 <= '0'; r1 <= '0'; x <= '0';

8

r2 <= (others => '0');

9

10

elsif rising_edge(clk) then

11

r0 <= a xor r1;

12

r1 <= r0;

x \leq r1;

13

r2 <= std_ulogic_vector(

signed(c) + signed(d)

15

);

16

17

end if;

end process;

18

```

semination and of multi-constit is seemed by the constitution of t

Hence, we simply add an appropriate connection to our circuit diagram.

# Example 2: Circuit - Registers

```

HWMod

WS24

```

```

1 architecture arch of code2circuit is

signal r0, r1 : std_ulogic;

signal r2 : c'subtype;

4 begin

process (clk, res_n)

begin

6

if res_n = '0' then

r0 <= '0'; r1 <= '0'; x <= '0';

8

r2 <= (others => '0');

9

10

elsif rising_edge(clk) then

11

r0 <= a xor r1;

12

r1 <= r0;

x \leq r1;

13

14

r2 <= std_ulogic_vector(

signed(c) + signed(d)

15

16

);

17

end if;

end process;

18

```

The signal  $\ensuremath{\mathbf{x}}$  is handled in the exact same way.

# Example 2: Circuit - Registers

```

HWMod

WS24

```

```

1 architecture arch of code2circuit is

signal r0, r1 : std_ulogic;

signal r2 : c'subtype;

4 begin

process (clk, res_n)

begin

6

if res_n = '0' then

r0 <= '0'; r1 <= '0'; x <= '0';

8

r2 <= (others => '0');

9

10

elsif rising_edge(clk) then

11

r0 <= a xor r1;

12

r1 <= r0;

x <= r1;

13

14

r2 <= std_ulogic_vector(

signed(c) + signed(d)

15

);

16

17

end if;

end process;

18

```

For r0 the situation is slightly different, as here the right-hand side of the assignment contains an XOR-operation of two signals. However, the respective part of the circuit is still quite straight-forward to implement.

#### Example 2: Circuit - Registers

```

HWMod

WS24

```

```

1 architecture arch of code2circuit is

signal r0, r1 : std_ulogic;

signal r2 : c'subtype;

4 begin

process (clk, res_n)

begin

6

if res_n = '0' then

r0 <= '0'; r1 <= '0'; x <= '0';

8

r2 <= (others => '0');

9

10

elsif rising_edge(clk) then

r0 <= a xor r1;

11

r1 <= r0;

12

x \ll r1;

13

14

r2 <= std_ulogic_vector(

signed(c) + signed(d)

15

);

16

end if;

17

end process;

18

```

We simply add an XOR gate with the appropriate input signals to the input of the flip-flop that drives r0.

#### Example 2: Circuit - Registers

```

HWMod

WS24

```

```

1 architecture arch of code2circuit is

signal r0, r1 : std_ulogic;

signal r2 : c'subtype;

4 begin

process (clk, res_n)

begin

6

if res_n = '0' then

r0 <= '0'; r1 <= '0'; x <= '0';

8

r2 <= (others => '0');

9

10

elsif rising_edge(clk) then

r0 <= a xor r1;

11

12

r1 <= r0;

x \ll r1;

13

14

r2 <= std_ulogic_vector(

signed(c) + signed(d)

15

16

);

17

end if;

end process;

18

```

Finally, we have to deal with r2. However, this is essentially handled in the exact same way as the XOR gate.

#### Example 2: Circuit - Registers

```

HWMod

WS24

```

```

1 architecture arch of code2circuit is

signal r0, r1 : std_ulogic;

signal r2 : c'subtype;

4 begin

process (clk, res_n)

begin

6

if res_n = '0' then

r0 <= '0'; r1 <= '0'; x <= '0';

8

r2 <= (others => '0');

9

10

elsif rising_edge(clk) then

r0 <= a xor r1;

11

12

r1 <= r0;

x \ll r1;

13

14

r2 <= std_ulogic_vector(

signed(c) + signed(d)

15

);

16

17

end if;

end process;

18

```

```

From Circuits to Code and Back

VHDL → Circuit

Example 2: Circuit - Registers

```

We simply add an adder with the appropriate inputs to the register that drives r2. Notice that the adder produces an M-bit wide signal.

#### Example 2: Circuit - Registers

```

HWMod

WS24

```

```

1 architecture arch of code2circuit is

signal r0, r1 : std_ulogic;

signal r2 : c'subtype;

4 begin

process (clk, res_n)

begin

6

if res_n = '0' then

7

r0 <= '0'; r1 <= '0'; x <= '0';

8

r2 <= (others => '0');

9

10

elsif rising_edge(clk) then

r0 <= a xor r1;

11

12

r1 <= r0;

x \ll r1;

13

r2 <= std_ulogic_vector(

14

signed(c) + signed(d)

15

);

16

17

end if;

end process;

18

```

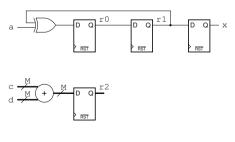

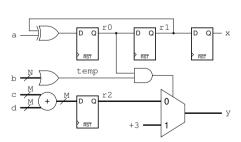

Now let's turn to the second process, which – as already mentioned – only contains combinational logic.

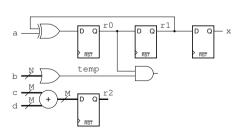

# Example 2: Circuit - Combinational Process

```

HWMod

WS24

```

```

process(all)

19

variable temp : std_ulogic;

20

21

temp := '0';

22

for i in b'range loop

temp := temp or b(i);

24

end loop;

25

26

y \le r2;

27

28

29

if temp and r0 then

y <= std_ulogic_vector(

30

to_unsigned(3, y'length)

31

32

);

end if;

33

34

end process;

35

36 end architecture;

```

# From Circuits to Code and Back VHDL → Circuit Example 2: Circuit - Combinational Process

The process initially sets the temporary single-bit variable temp to zero. It then uses a for-loop to go over all elements of the input b and calculates the disjunction with temp, which is then again assigned to the temp variable. Hence, if any of the elements of b is one, temp is set to one as well and will stay at that value until the end of the loop.

### Example 2: Circuit - Combinational Process

```

HWMod

WS24

```

```

process(all)

19

variable temp : std_ulogic;

20

21

temp := '0';

22

for i in b'range loop

temp := temp or b(i);

24

end loop;

25

26

27

y \ll r2;

28

if temp and r0 then

29

y <= std_ulogic_vector(

30

to_unsigned(3, y'length)

31

32

);

end if:

end process;

34

35

36 end architecture;

```

Notice how this effectively describes an N-input OR gate with temp as its output signal.

# Example 2: Circuit - Combinational Process

```

HWMod

WS24

```

```

process(all)

19

variable temp : std_ulogic;

20

21

temp := '0';

22

for i in b'range loop

temp := temp or b(i);

24

end loop;

25

26

y \le r2;

27

28

29

if temp and r0 then

y <= std_ulogic_vector(

30

to_unsigned(3, y'length)

31

32

);

end if;

33

34

end process;

35

36 end architecture;

```

# From Circuits to Code and Back VHDL → Circuit Example 2: Circuit - Combinational Process

The next part of the process contains an if-statement. First y is assigned the value of  $x^2$ . If the if-condition is true this value is then overridden by the constant three. Notice that it would be semantically equivalent to perform the  $x^2$  assignment in the else-branch of the if statement. We already know that if-statements can be expressed using multiplexers. However, before we can do that we have to generate a signal that we can feed into the control input of this multiplexer.

## Example 2: Circuit - Combinational Process

```

HWMod

WS24

```

```

process(all)

19

variable temp : std ulogic;

20

21

temp := '0';

22

for i in b'range loop

temp := temp or b(i);

24

end loop;

25

26

27

v \le r2:

28

if temp and r0 then

29

y <= std_ulogic_vector(

30

to_unsigned(3, y'length)

31

32

);

end if;

end process;

34

35

36 end architecture;

```

For that purpose we add an AND gate, that evaluates the conjunction used by the expression in the if-condition.

# Example 2: Circuit - Combinational Process

```

HWMod

WS24

```

```

process(all)

19

variable temp : std_ulogic;

20

21

temp := '0';

22

for i in b'range loop

temp := temp or b(i);

24

end loop;

25

26

y \le r2;

27

28

if temp and r0 then

29

y <= std_ulogic_vector(

30

to_unsigned(3, y'length)

31

32

);

end if;

33

34

end process;

35

36 end architecture;

```

Finally we can use the output signal of this "AND" gate to control the multiplexer that produces the output y of our circuit. And with that our circuit diagram is complete.

### Example 2: Circuit - Combinational Process

```

HWMod

WS24

```

```

process(all)

19

variable temp : std_ulogic;

20

21

temp := '0';

22

for i in b'range loop

temp := temp or b(i);

24

end loop;

25

26

y \le r2;

27

28

29

if temp and r0 then

y <= std_ulogic_vector(

30

to_unsigned(3, y'length)

31

32

);

end if;

33

34

end process;

35

36 end architecture;

```

Thank you for listening! We recommend you to immediately take the self-check test in TUWEL, to see if you understood the material presented in this lecture.

C2C

Introduction

Circuit → VHDL

VHDL → Circuit

Entity

Architecture

# Lecture Complete!