In this lecture we will discuss synthesizable processes, which can be used to describe hardware using sequential statements.

Modified: 2025-03-20, 14:05 (830283c)

# -Behavioral Modeling

| Concurrent assignments and structural modeling     Can model all combinational hardware     Hardly scales |                      |                             |                 |            |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------|----------------------|-----------------------------|-----------------|------------|--|--|--|--|

|                                                                                                           |                      | Behavior                    | Sinahare        | Generatory |  |  |  |  |

|                                                                                                           | Spilen Level         | 10.10*                      | 200             | 80         |  |  |  |  |

|                                                                                                           | Algorithmic<br>Level |                             | 2               | × 4        |  |  |  |  |

|                                                                                                           | Level (RTL)          | 1111                        | 276             | фф         |  |  |  |  |

|                                                                                                           | Lagis Lawel          | 8 - 1073<br>7 - 10700, 0001 | :=0i0-          | 日告         |  |  |  |  |

|                                                                                                           | Creat Level          | ****                        | <b>ध्वर^र्व</b> | 主臣         |  |  |  |  |

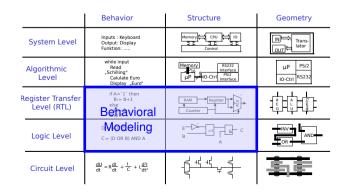

In previous lectures we have discussed how hardware can be described by using concurrent signal assignments and structural modeling. This combination already allows us to describe arbitrary combinational hardware. However, it hardly scales. Think about arithmetic logic units in CPUs which are used to perform computations. Although it is only combination, it can become quite complex and while we \*could\* describe it with the means we discussed so far, it would not be a very pleasant experience. The reason being that we are not really describing our hardware programmatically on the register-transfer-level as we would ideally do. Obviously, we need a method for modeling circuits with a complex behavior.

### Introduction

HWMod WS24

Beh. Mod. Introduction About Example Sensitivity Process Simulatio Variables Remarks

- Concurrent assignments and structural modeling

- Can model all combinational hardware

- Hardly scales...

|                                  | Behavior                                                              | Structure                                                                              | Geometry                 |

|----------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------|

| System Level                     | Inputs : Keyboard<br>Output: Display<br>Funktion:                     |                                                                                        |                          |

| Algorithmic<br>Level             | while input<br>Read<br>"Schilling"<br>Calulate Euro<br>Display "Euro" | Memory<br>A 16<br>Memory<br>Interface<br>Memory<br>Interface<br>Interface<br>Interface | μΡ P5/2<br>IO-Ctrl R5232 |

| Register Transfer<br>Level (RTL) | if A=`1` then<br>B:= B+1<br>else<br>B:= B<br>end if                   | RAM Register                                                                           |                          |

| Logic Level                      | D = NOT E<br>C = (D OR B) AND A                                       | B A C                                                                                  |                          |

| Circuit Level                    | $\frac{dU}{dt} = R\frac{dI}{dt} + \frac{I}{C} + L\frac{d^2I}{dt^2}$   | ┤ <mark>┽╡╶┽╡╶┽╴╶┽╡</mark><br>┤ <sub>┥</sub> ╡╴╴╤╴┥╡                                   | 事車                       |

### -Behavioral Modeling └─Introduction └─Introduction

| Can I | Concurrent assignments and structural modeling<br>Can model all combinational hardware<br>Hardly scaleshow? |                            |           |            |  |  |  |  |

|-------|-------------------------------------------------------------------------------------------------------------|----------------------------|-----------|------------|--|--|--|--|

|       |                                                                                                             | Behavior                   | Dirachare | Generatory |  |  |  |  |

|       | lysten invel                                                                                                | 100.100*                   | 200       | 80         |  |  |  |  |

| 1.1   | Level .                                                                                                     |                            | 200       | × 10       |  |  |  |  |

|       | Caral (UL)                                                                                                  | ?                          |           | фф         |  |  |  |  |

|       | Legis Level                                                                                                 | 1 - 1075<br>7 - 1156 (1074 | :=0i0-    | <b>日</b> 目 |  |  |  |  |

|       | Crowl Level                                                                                                 | ****                       | Que à     | 車車         |  |  |  |  |

It would be nice if we could make use of the control flow statements we introduced in the lecture about VHDL basics Furthermore, it is desirable that we can encapsulate parts of a complex design in distinct structures, without the need to create a new entity and architecture and to instantiate it. Additionally, as we as humans try to break complex behavior down in sequences of simpler behavior, we would desire a means to describe our circuits sequentially.

### Introduction

HWMod WS24

Beh. Mod. Introduction About Example Sensitivity Process Simulation Variables Remarks

- Concurrent assignments and structural modeling

- Can model all combinational hardware

- Hardly scales...how?

|                                  | Behavior                                                              | Structure                                             | Geometry                 |

|----------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------|--------------------------|

| System Level                     | Inputs : Keyboard<br>Output: Display<br>Funktion:                     |                                                       |                          |

| Algorithmic<br>Level             | while input<br>Read<br>"Schilling"<br>Calulate Euro<br>Display "Euro" | Memory<br>16<br>16<br>16<br>10-Ctrl PS/2<br>Interface | μΡ P5/2<br>IO-Ctrl R5232 |

| Register Transfer<br>Level (RTL) | if A=`1` then<br>B:= 571<br>else<br>B:= 5<br>end if                   | RAM Register                                          |                          |

| Logic Level                      | D = NOT E<br>C = (D OR B) AND A                                       |                                                       |                          |

| Circuit Level                    | $\frac{dU}{dt} = R\frac{dI}{dt} + \frac{I}{C} + L\frac{d^2I}{dt^2}$   | ╢ <mark>╡┽╡╺╡</mark> ╶┥╡<br>╢┥<br>╶                   | 事業                       |

-Behavioral Modeling └─Introduction └─Introduction

|                                  | Relation    | Seature | Generatory |

|----------------------------------|-------------|---------|------------|

| System Level                     | 10.10*      | 200     | 80         |

| Algorithmic<br>Local             |             | 2       | × 10       |

| Legislar Transfer<br>Level (NTL) | Betstvioral |         | фф         |

| Logic Level                      | Modeling    | :==010  | <b>日</b> 目 |

| Creat Level                      | ****        | fee*f   | <u>事</u> 業 |

This is where behavioral modeling comes in.

### Introduction

### HWMod WS24

Beh. Mod. Introduction About Example Sensitivity Process Simulation Variables Remarks

- Concurrent assignments and structural modeling

- Can model all combinational hardware

- Hardly scales...how?

- ⇒ Behavioral Modeling

### -Behavioral Modeling └─Introduction └─**Behavioral Modeling**

L

Revolves around processes

Must be synthesizable

In a nutshell, behavioral modeling allows us to use synthesizable processes to describe our hardware.

#

# ─Behavioral Modeling └─Introduction └─Behavioral Modeling

Revolves around processes

Must be synthesizable

"single-use entity and architecture

Up to some extent, we can picture such synthesizable processes to be an inline entity and architecture. That is, we can split our model into functionally loosely connected submodules in a much more concise manner than by creating distinct entities and instantiating them.

### HWMod WS24 Beh.Mod. Hwodukard Example SonstWit Variables Remerki

### -Behavioral Modeling └─Introduction └─**Behavioral Modeling**

Revolves around processes

Must be synthesizable

"single-use entity and architecture"

Control flow statements and variables

Sequential description

We can also use control flow statements inside processes, thus giving us access to if, case and even loop statements. Furthermore, we can use variables and describe our circuits in a somewhat sequential manner. We will discuss both in detail during this lecture.

### Behavioral Modeling Brudd Ward Bread Bread

# ─Behavioral Modeling └─Introduction └─Behavioral Modeling

Revolves around processes III Must be synthesizable "single-use enthy and architecture" III Control flow statements and variables IIII Sequential discription Complements struct. modeling and concurrent assignments

However, it must be stressed that behavioral modeling is not an alternative to structural modeling and concurrent assignments but rather a powerful complement. Typically, you would use all three methods throughout a design.

# Evended Vorses Provide Vorses Provid

### -Behavioral Modeling └─Introduction └─**Behavioral Modeling**

Perolves around processes

Must be synthesizable

Single-use ently and architecture

Single-use ently and architecture

Single-use ently and architecture

Complements struct: modeling and concurrent assignments

Ubguldous in synchronous designs

Furthermore, as we will see in chapter 3, behavioral modeling is ubiquitous in synchronous designs as it allows for very concise and maintainable description of such circuits. We will now look at a first example of how a behavioral model of a circuit looks like and then elaborate on its details.

### HWMod Wsz4 Beh. Mod Wsz4 Beh. Mod Wsz4 Ben. Must be synthesizable Ben. Must be synthesizable Ben. Must be synthesizable Ben. Must be synthesizable Ben. Control flow statements and variables Bequential description Becomplements struct. modeling and concurrent assignments Beliquitous in synchronous designs

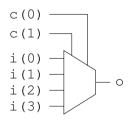

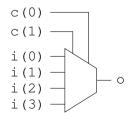

Recall the implementation of a simple 4:1 multiplexer that you saw in the lecture about entities and architectures. The slide shows the respective implementation based on concurrent signal assignments. Let us now apply our already gathered knowledge and rewrite this implementation as a process. In a first attempt we could make use of the case statement to describe the select logic of the multiplexer in a more comprehensible manner.

### Example: Multiplexer

1 entity mux41 is

HWMod WS24

Seh. Mod. Introduction About Example Sensitivity Process Simulatio Variables Remarks

```

port (

2

c : in boolean_vector(1 downto 0);

3

i : in boolean vector(3 downto 0);

4

o : out boolean

5

);

6

7 end entity;

1 architecture csa of mux_41 is

2 begin

o \le i(0) when not c(1) and not c(0) else

3

4

i(1) when not c(1) and

c(0) else

5

i(2) when

c(1) and not c(0) else

i(3) when

c(1) and

c(0);

6

7 end architecture;

```

This is shown on the slide. We use a case statement to determine the output based on the control signal c and complete the process with a wait statement. So far so good, right?

### Example: Multiplexer

1 entity mux41 is

```

HWMod

WS24

```

Seh. Mod. Introduction About Example Sensitivity Process Simulation Variables Remarks

```

2 port (

c : in boolean_vector(1 downto 0);

3

i : in boolean vector(3 downto 0);

4

o : out boolean

5

);

6

7 end entity;

1 architecture beh of mux_41 is

2 begin

3 process begin

case c is

4

when false & false => o <= i(0);

5

when false & true => o <= i(1);</pre>

6

when true & false => o <= i(2);

7

when true & true => o <= i(3);</pre>

8

9

end case;

10

wait;

11

end process;

12 end architecture;

```

When we initially introduced processes, we did not really motivate the wait statement that we always put at the end of their bodies. We just stated that it is required for the process to terminate.

### Example: Multiplexer

1 entity mux41 is

HWMod WS24

Beh. Mod. Introduction About Example Sensitivity Process Simulation Variables Remarks

```

2 port (

3 c : in boolean_vector(1 downto 0);

i : in boolean vector(3 downto 0);

4

o : out boolean

5

6);

7 end entity;

1 architecture beh of mux_41 is

2 begin

3 process begin

case c is

4

when false & false => o <= i(0);</pre>

5

6 when false & true => o <= i(1);</pre>

7

when true & false => o <= i(2);

when true & true => o <= i(3);</pre>

8

9

end case;

10

wait;

11 end process;

12 end architecture;

```

However, while this might be sensible for a sequential piece of code executed during simulation, it hardly makes sense for describing a circuit. After all, exactly what hardware behavior is this supposed to model?

### Example: Multiplexer

HWMod WS24

Beh. Mod. Introduction About Example Sensitivity Process Simulatio Variables Remarks

```

1 entity mux41 is

2 port (

c : in boolean_vector(1 downto 0);

3

i : in boolean vector(3 downto 0);

4

o : out boolean

5

6);

7 end entity;

1 architecture beh of mux_41 is

2 begin

3 process begin

case c is

4

when false & false => o <= i(0);</pre>

5

when false & true => o <= i(1);</pre>

6

7

when true & false => o <= i(2);

when true & true => o <= i(3);</pre>

8

9

end case;

\Rightarrow "Termination" of circuit?!

10

wait;

11 end process;

12 end architecture;

```

While termination is something a program might do, a circuit will always be active unless its power is cut. This is why a process with the simple wait statement we used so far is *not synthesizable* nd should therefore not be used to describe hardware.

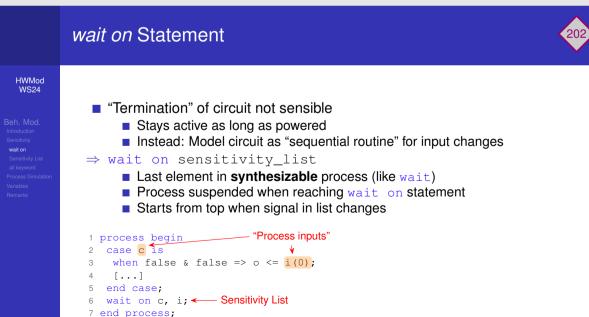

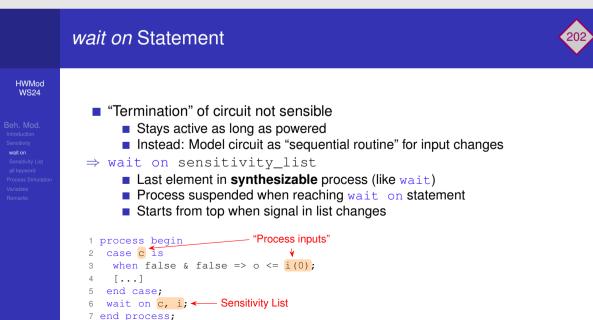

### wait on Statement

HWMod WS24

Beh. Mod. Introduction Sensitivity wait on Sensitivity List all keyword Process Simulati Variables Remarks

- "Termination" of circuit not sensible

- Stays active as long as powered

"Termination" of circuit not sensible Stays active as long as powered Instead: Model circuit as "sequential routine" for input changes If we think about our multiplexer, it simply maps its inputs i and c to its output o. Hence, whenever an input changes the circuit's output might change as well. In behavioral modeling we capture this as a sequential routine that is applied whenever an input changes. However, note that this is just an abstraction for describing a concurrent circuit! In reality there is neither a routine nor a sequential execution of our model.

### wait on Statement

Beh. Mod. Introduction Sensitivity wait on Sensitivity List all keyword Process Simulation Variables Remarks

- "Termination" of circuit not sensible

- Stays active as long as powered

- Instead: Model circuit as "sequential routine" for input changes

"Termination" of circuit not sensible

Bitys active as long as powered

Instead: Model circuit as "sequential routine" for input changes

wait on sensitivity\_list

The way we can capture this *sensitivity* o certain signals is using the wait on instead of the wait statement. This statement contains a, so-called, *sensitivity list* f signals to which the respective process is sensitive. Note that we refer to a process being sensitive to a signal when it reads it somewhere inside its body.

### wait on Statement

### HWMod WS24

Beh. Mod. Introduction Sensitivity wait on Sensitivity List all keyword Process Simulation Variables Remarks

- "Termination" of circuit not sensible

- Stays active as long as powered

- Instead: Model circuit as "sequential routine" for input changes

- ⇒ wait on sensitivity\_list

"Termination" of circuit not sensible Bistya active as long as powered Instead: Model circuit as "sequential routine" for input changes with on sensitivity\_list Bistelement is synthesizable process (Wke writ) In our code we simply replace the single wait statement we had at the end processes before by a fitting wait on statement.

# wait on Statement HWMod WS24

- "Termination" of circuit not sensible

- Stays active as long as powered

- Instead: Model circuit as "sequential routine" for input changes

### ⇒ wait on sensitivity\_list

Last element in synthesizable process (like wait)

"Termination" of circuit not sensible ■ Stays active as long as powered ■ Instead: Model circuit as "sequential routine" for input changes wait on sensitivity\_list ■ Last element in synthesizable process (Ne vsit) ■ Process supported when reacting usit on statement Thinking about a circuit, we can picture this statement to a check whether all inputs, and thus also the outputs, of the described circuit are stable. Only when an input changes, the output might change, which is modeled by the statements inside the process above the wait statement. In a simulation, this is achieved by letting the wait on statement suspend the process.

### wait on Statement

### HWMod WS24

Seh. Mod. Introduction Sensitivity wait on Sensitivity List all keyword Process Simulatic Variables Remarks

- "Termination" of circuit not sensible

- Stays active as long as powered

- Instead: Model circuit as "sequential routine" for input changes

### ⇒ wait on sensitivity\_list

- Last element in synthesizable process (like wait)

- Process suspended when reaching wait on statement

"Termination" of circuit not sensible ID Stays active as long as powered IN Instand: Model circuit as "sequential routine" for input changes wait on sensitivity\_list I ast diement in synthesizable process (like wait) IP Process suspended when reaching wait on statement IP Starts from to when signal int changes The process is only woken up again when a signal on the sensitivity list changes. Once this happens, the process is executed again from top to bottom. We can thus sort of think about a process as the mentioned routine for reacting to input changes.

# wait on Statement

### HWMod WS24

Beh. Mod. Introduction Sensitivity wait on Sensitivity List all keyword Process Simulatio Variables Remarks

- "Termination" of circuit not sensible

- Stays active as long as powered

- Instead: Model circuit as "sequential routine" for input changes

### $\Rightarrow$ wait on sensitivity\_list

- Last element in synthesizable process (like wait)

- Process suspended when reaching wait on statement

- Starts from top when signal in list changes

"Termination" of circuit not sensable

Bype after as tops a power and manafer for the of damps of the sensation of the senset of the sensation of the senset of the sensation of the sena

Let us have a look at the multiplexer process from the previous slide, with this change in-place. The process only drives the signal  $\circ$ , depending on the signals  $\pm$  and c. We can think of these two signals as being the inputs of the process. Therefore, our process is sensitive to changes of these two signals.

### wait on Statement HWMod **WS24** "Termination" of circuit not sensible Stays active as long as powered Instead: Model circuit as "sequential routine" for input changes wait on $\Rightarrow$ wait on sensitivity\_list Last element in synthesizable process (like wait) Process suspended when reaching wait on statement Starts from top when signal in list changes 1 process begin 2 case c is 3 when false & false => o <= i(0);</pre> 4 [...] 5 end case; 6 wait on c, i; 7 end process;

## ─Behavioral Modeling └─Sensitivity

*wait on* Statement

4

### ─Behavioral Modeling └─Sensitivity

*wait on* Statement

With the sensitivity list describing to which signals the circuit modelled by a process is sensitive to, its completeness is of course paramount. We will now demonstrate this at the hand of an example.

Completeness of sensitivity list matters

### Example: Half-adder

HWMod WS24

Seh. Mod. Introduction Sensitivity wait on Sensitivity List all keyword Process Simulatio Variables Remarks

Completeness of sensitivity list matters!

Consider the half-adder shown on the slide, featuring two inputs a and b, and two outputs s and c. The respective entity does therefore contain exactly these four ports. The circuit itself is quite simple with each output being generated from the two inputs via a single gate.

### Example: Half-adder

HWMod WS24

Seh. Mod. Introduction Sensitivity wait on Sensitivity List all keyword Process Simulatic Variables Remarks

### Completeness of sensitivity list matters!

1 entity ha is

2 port (

3 a, b : in boolean;

4 s, c : out boolean

5 );

6 end entity;

Completeness of sensitivity ist mattered

We can write a behavioral model of the half-adder as shown on the slide, consisting of a single process that drives the two outputs.

### Example: Half-adder

1 entity ha is

### HWMod WS24

Seh. Mod. Introduction Sensitivity wait on Sensitivity List all keyword Process Simulatio Variables Remarks

```

2 port (

a, b : in boolean;

3

s, c : out boolean

4

5);

6 end entity;

1 architecture arch1 of ha is

2 begin

3 process begin

4 s <= a xor b;

5 c <= a and b;

6

wait on a, b;

7 end process;

8 end architecture;

```

Completioness of sensitivity let mattered

Since the behavior modeled by this process is sensitive to both a and b, the process ends with a wait on statement sensitive to these two signals.

### Example: Half-adder

1 entity ha is

### HWMod WS24

Seh. Mod. Introduction Sensitivity wait on Sensitivity List all keyword Process Simulatio Variables Remarks

```

2 port (

a, b : in boolean;

3

s, c : out boolean

4

5);

6 end entity;

1 architecture arch1 of ha is

2 begin

3 process begin

4 s <= a xor b;

5 c <= a and b;

6

wait on a, b;

7 end process;

8 end architecture;

```

Consider the result of simulating this implementation, where we called the outputs c1 and s1 for later comparison. We can observe a sequence of inputs and the respective sequence of outputs generated by our circuit. For the simple half adder, with only four possible combinations of inputs, we can immediately observe that our implementation is correct.

### Example: Half-adder

1 entity ha is

### HWMod WS24

Seh. Mod. Introduction Sensitivity wait on Sensitivity List all keyword Process Simulation Variables Remarks

| 2 | port (                      |

|---|-----------------------------|

| 3 | a, b : in boolean;          |

| 4 | s, c : out boolean          |

| 5 | );                          |

| 6 | end entity;                 |

|   |                             |

| 1 | architecture arch1 of ha is |

| 2 | begin                       |

| 3 | process begin               |

| 4 | s <= a xor b;               |

| 5 | c <= a and b;               |

| 6 | wait on a, b;               |

| 7 | end process;                |

| 8 | end architecture;           |

However, what if we forgot a signal, in the example on the slide b, when writing the sensitivity list?

### Example: Half-adder

1 entity ha is

### HWMod WS24

Seh. Mod. Introduction Sensitivity wait on Sensitivity List all keyword Process Simulation Variables Remarks

|   | -                           |

|---|-----------------------------|

| 2 | port (                      |

| 3 | a, b : in boolean;          |

| 4 | s, c : out boolean          |

| 5 | );                          |

| 6 | end entity;                 |

|   |                             |

| 1 | architecture arch2 of ha is |

|   | begin                       |

| ~ | begin                       |

| 3 | process begin               |

| 4 | s <= a xor b;               |

| 5 | c <= a and b;               |

| 6 | wait on <mark>a</mark> ;    |

| 7 | end process;                |

| 8 | end architecture;           |

| 🧇 a             | TRUE  |  |  |  |  |

|-----------------|-------|--|--|--|--|

| - 🧇 b           | TRUE  |  |  |  |  |

| — wait on a, b; |       |  |  |  |  |

| 🔷 c1            | TRUE  |  |  |  |  |

| 🧇 s1            | FALSE |  |  |  |  |

If we simulate this modified implementation using the same input sequence as before, and look at the output traces  $c_2$  and  $s_2$ , we can observe that this implementation is **not** correct when simulated! Of course, this deviation from the desired circuit has its origin in the fact that our model is not sensitive to changes of the input b, although its output might change due a change of b only.

### Example: Half-adder

1 entity ha is

### HWMod WS24

Seh. Mod. Introduction Sensitivity wait on Sensitivity List all keyword Process Simulation Variables Remarks

| 2 | port (                      |

|---|-----------------------------|

| 3 | a, b : in boolean;          |

| 4 | s, c : out boolean          |

| 5 | );                          |

| 6 | end entity;                 |

|   |                             |

| 1 | architecture arch2 of ha is |

| 2 | begin                       |

| 3 | process begin               |

| 4 | s <= a xor b;               |

| 5 | c <= a and b;               |

| 6 | wait on a;                  |

| 7 | end process;                |

| 8 | end architecture;           |

| 🔶 a             | TRUE          |  |  |  |  |

|-----------------|---------------|--|--|--|--|

| 🧇 b             | TRUE          |  |  |  |  |

| — wait on a, b; | -             |  |  |  |  |

|                 | TRUE<br>FALSE |  |  |  |  |

| — wait on a; —  | FALSE         |  |  |  |  |

| 4 c2            | FALSE         |  |  |  |  |

| 🔶 s2            | TRUE          |  |  |  |  |

In conclusion, always keep in mind to what signals your processes should be sensitive to and write your sensitivity accordingly.

### Example: Half-adder

1 entity ha is

### HWMod WS24

Seh. Mod. Introduction Sensitivity wait on Sensitivity List all keyword Process Simulation Variables Remarks

| 2 port (                      |

|-------------------------------|

| 3 a, b : in boolean;          |

| 4 s, c : out boolean          |

| 5 );                          |

| 6 end entity;                 |

|                               |

| 1 architecture arch2 of ha is |

| 2 begin                       |

| 3 process begin               |

| 4 s <= a xor b;               |

| 5 c <= a and b;               |

| 6 wait on a;                  |

| 7 end process;                |

| 8 end architecture;           |

| 🧇 a             | TRUE  |  |  |  |  |

|-----------------|-------|--|--|--|--|

|                 | TRUE  |  |  |  |  |

| — wait on a, b; |       |  |  |  |  |

| 🔶 c1            | TRUE  |  |  |  |  |

| 🧇 s1            | FALSE |  |  |  |  |

| — wait on a; —  |       |  |  |  |  |

|                 | FALSE |  |  |  |  |

| 🔷 s2            | TRUE  |  |  |  |  |

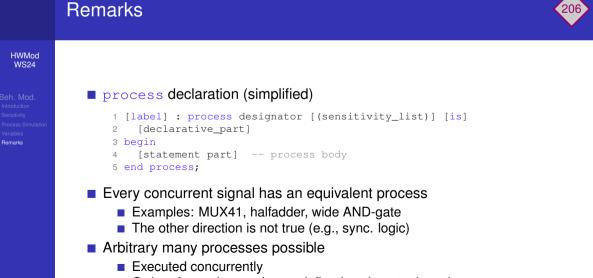

On the previous slides we have seen how we can replace the wait statement at the end of a process by a wait on statement. And while this can model the behavior we actually want, there exists an equivalent alternative to the wait on that is usually preferred. We will now look at this alternative.

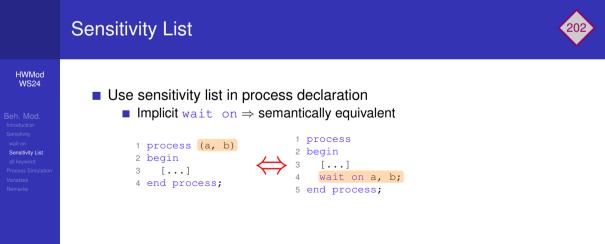

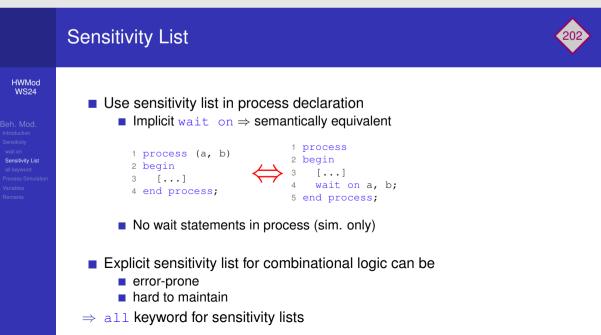

### Sensitivity List

6

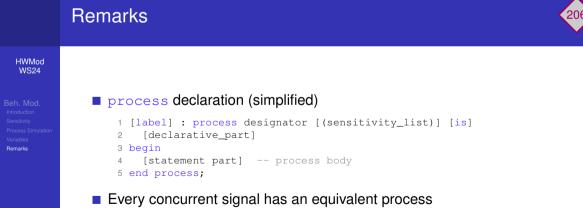

WX2d Benaltory Wataon Senaltory Watabas Remarks

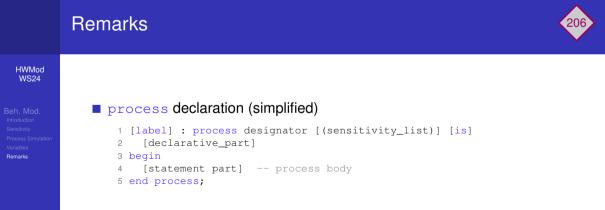

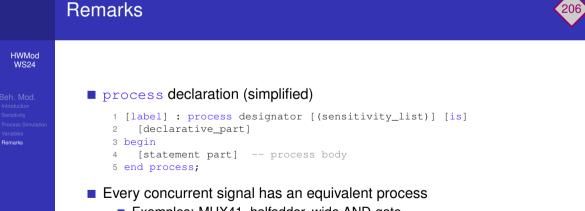

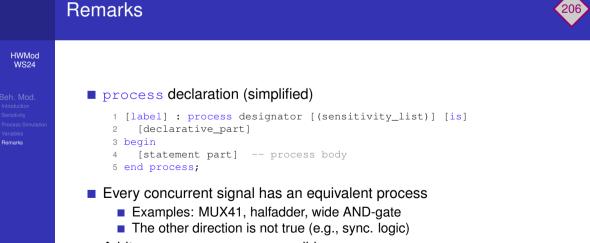

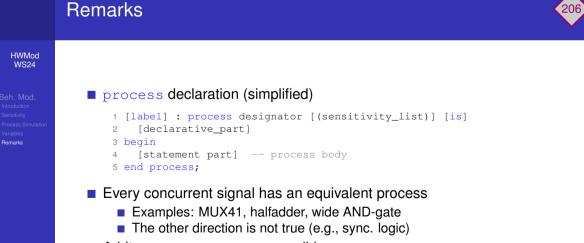

Instead of writing an explicit wait on statement with a sensitivity list as the last element of a process, we can also define the sensitivity list as part of the process declaration itself.

### Sensitivity List

Use sensitivity list in process declaration

■ Implicit wait on ⇒ semantically equivalent

Beh. Mod. Introduction Sensitivity wait on Sensitivity List all keyword Process Simulation Variables Remarks

The code snippet shown on the slide demonstrates this for the half-adder implementation you just saw.

# Sensitivity List WWod MV Mod Not Model wasted wast

This implicitly expresses the respective wait on statement implicitly, resulting in sensitivity lists in process declarations and dedicated wait on statements being equivalent to each other.

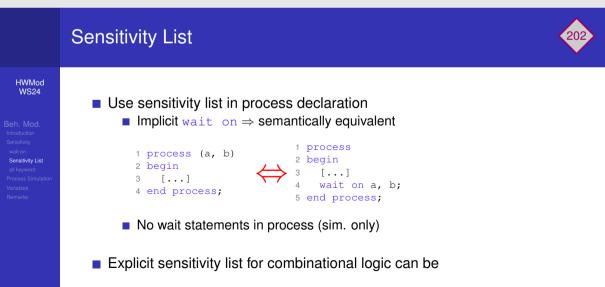

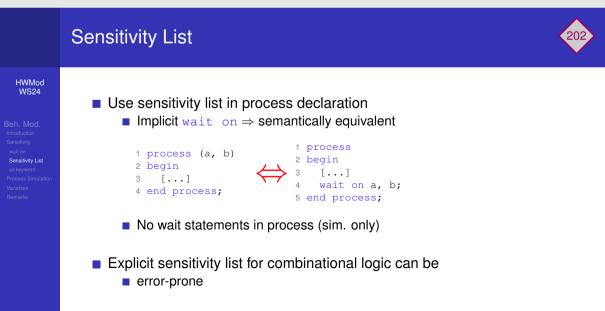

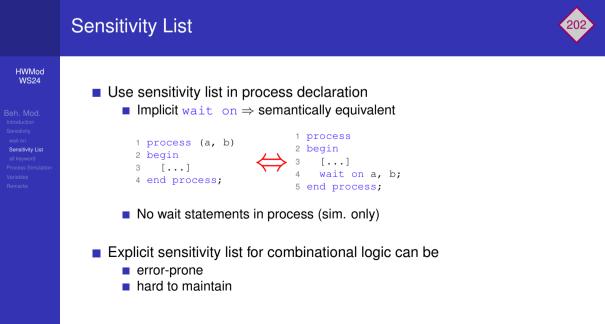

However, we want to point out that there is a consequence of using a sensitivity list in a process declaration and the explicit wait on. In particular, the standard states that processes with a sensitivity list must not contain any explicit wait statements.

### Sensitivity List HWMod **WS24** Use sensitivity list in process declaration Implicit wait on $\Rightarrow$ semantically equivalent 1 process 1 process (a, b) 2 begin 2 begin 3 [...] 3 [...] 4 wait on a, b; 4 end process; 5 end process; No wait statements in process (sim. only)

However, before that let us briefly discuss some properties of sensitivity lists.

6

### ─Behavioral Modeling └─Sensitivity └─Sensitivity List

Use sensibility list in process declaration

Implicit sent, to assessmentarially equivalent

I provide the sensibility of the combinational logic can be array process.

Think about a circuit with many inputs that is so complex that you *have* o split it into many multiple processes in order to keep your code readable and maintainable. Obviously, creating sensitivity lists for all of them can be quite error-prone, especially if there are many sensitivities.

## ─Behavioral Modeling └─Sensitivity └─Sensitivity List

Furthermore, the maintainability of sensitivity lists is also not particularly good. Whenever you rename a signal, you have to rename it in all sensitivity lists as well.

## ─Behavioral Modeling └─Sensitivity └─Sensitivity List

As a remedy the VHDL-2008 standard introduced the all keyword for sensitivity lists. We will discuss it on the next slide.

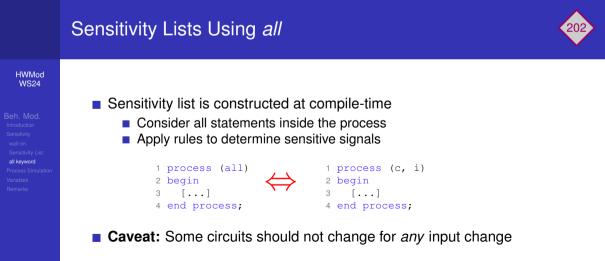

Sensitivity list is constructed at compile-time

Consider all statements inside the process

Apply rules to determine sensitive signals

By using the all keyword, the tools determine all signal sensitivities automatically. This is done by recursively considering all statements in a process and applying the rules defined in the standard to determine the sensitivities of all statements. The resulting sensitivity list is then the union of all these sensitivities.

## Sensitivity Lists Using all

#### HWMod WS24

Seh. Mod. Introduction Sensitivity wait on Sensitivity List all keyword Process Simulatio Variables Remarks

- Sensitivity list is constructed at compile-time

- Consider all statements inside the process

- Apply rules to determine sensitive signals

Sensitivity list is constructed at compile-time **E** Consider all tatements inside the process **B** Apply rules to determine sensitive signals  $\frac{1}{2} \frac{presenses}{1 + (-1)} \iff \frac{1}{2} \frac{presenses}{1 + (-1)} = \frac{1}{2} \frac{presens}{1$  On the slide you are shown how using this keyword would lookk like for the half-adder circuit and that this is equivalent to the sensitivity list we saw on the previous slide. However, if the tools are able to automatically determine all sensitivities, why shouldn't we always use this?

## Sensitivity Lists Using all

Beh. Mod. Introduction Sensitivity wait on Sensitivity List all keyword Process Simulatio Variables Remarks

- Consider all statements inside the process

- Apply rules to determine sensitive signals

```

1 process (all)

2 begin

3 [...]

4 end process;

```

```

1 process (c, i)

2 begin

3 [...]

4 end process;

```

Well, there is a caveat with using the all keyword, as not all incuits should react to any nput change.

■ Sensitivity list is constructed at completime ■ Consider all statements insiste the process ■ Apply rules between iterative statements insiste ■ apply rules between iterative statements in the statement ■ apply rules between iterative statements in the statement ■ Sensitivity and the statement is statement between iterative is and ■ Sensitivity in the statement is statement between iterative is and ■ Sensitivity in the statement is statement between iterative is and ■ Sensitivity in the statement is statement between iterative is and the statement is and the For example, synchronous circuits are only supposed to change when their clock or reset input changes. Changes of other inputs should never lead to a changed output on their own. We will elaborate further on this in the next chapter where we are concerned with synchronous logic.

#### Sensitivity Lists Using all HWMod **WS24** Sensitivity list is constructed at compile-time Consider all statements inside the process Apply rules to determine sensitive signals all keyword 1 process (all) 1 process (c, i) 2 begin 2 begin 3 [...] 3 [...] 4 end process; 4 end process; **Caveat:** Some circuits should not change for *any* input change Synchronous logic only sensitive to clock and reset More on that in chapter II

For now you can simply remember the rule of thumb that you can use the all keyword whenever you write a process that exclusively describes combinational logic.

### Sensitivity Lists Using all HWMod **WS24** Sensitivity list is constructed at compile-time Consider all statements inside the process Apply rules to determine sensitive signals all keyword 1 process (all) 1 process (c, i) 2 begin 2 begin 3 [...] 3 [...] 4 end process; 4 end process; Caveat: Some circuits should not change for any input change Synchronous logic only sensitive to clock and reset More on that in chapter II Rule of thumb: Use all for comb. processes

Process is a sequential description

Hardware is highly concurrent

If you recall the very first lecture, you might ask yourself what we mean when we state that behavioral modeling allows sequential description of circuits. After all, the hardware we model is still highly concurrent.

## **Process Simulation**

#### HWMod WS24

Beh. Mod. Introduction Sensitivity Process Simulation Example Observations Variables Remarks Process is a sequential description

Hardware is highly concurrent

### -Behavioral Modeling └-Process Simulation └-**Process Simulation**

Process is a sequential description

Hardware is highly concurrent

What does the simulator do?

The thing is that while processes do actually look a lot like sequential programs, the tools do not interpret them this way. Understanding what the tools actually do, given a process, is key when describing the behavior of hardware. We will now address how processes are simulated such that they mimic the behavior to concurrent hardware, leaving the treatment of synthesis for a future lecture.

## **Process Simulation**

#### HWMod WS24

Beh. Mod. Introduction Sensitivity Process Simulation Example Observations Variables Remarks

- Process is a *sequential* description

- Hardware is highly concurrent

- What does the simulator do?

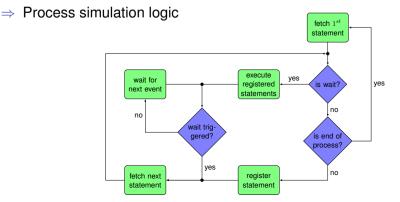

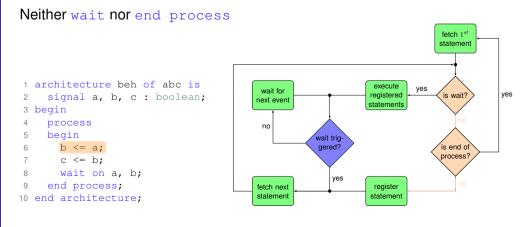

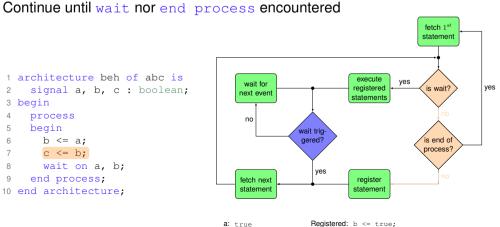

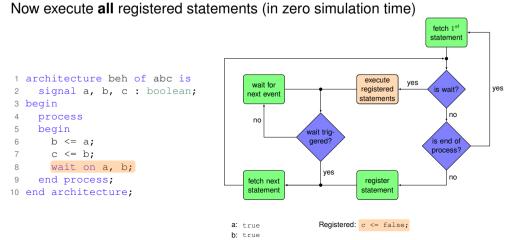

The flowchart on the slide captures the essential process simulation logic used by a simulator. Green boxes express an action taken by the simulator, blue diamonds mark decisions. At such decision nodes the out-going edges are annotated with the respective decision outcome. Since this process simulation logic is quite intricate, we will break it down using an example during the next few slides.

## **Process Simulation**

#### HWMod WS24

Beh. Mod. Introduction Sensitivity Process Simulation Example Observations Variables Remarks

- Process is a sequential description

- Hardware is highly concurrent

- What does the simulator do?

1 architecture beh of abs is

2 signal A, b, d : booleany

3 begin

4 provide the second se

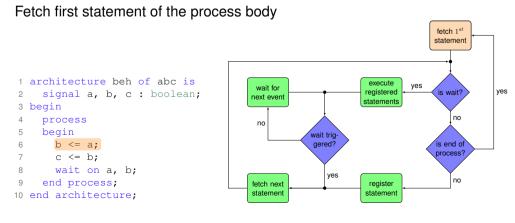

Let us consider the example architecture shown on the slide. It comprises three signals a, b and c and a process that drives b and c.

#### **Example: Process Simulation** HWMod **WS24** 1 architecture beh of abc is Example signal a, b, c : boolean; 2 3 begin 4 process 5 begin 6 b <= a; 7 c <= b; 8 wait on a, b; 9 end process; 10 end architecture;

L

1 architesture beh of abo is 2 architesture beh of abo is 3 begin 4 proba 5 begin 5 begin 5 begin 6 proba 7  $0 \ll h_0$ 8 begin 9 end probasy 9 en

If you apply what you heard before, you can immediately observe that the process is sensitive to a and b.

### **Example: Process Simulation** HWMod **WS24** Example 1 architecture beh of abc is signal a, b, c : boolean; 2 3 begin 4 process 5 begin 6 b <= a; c <= b; 7 wait on a, b; 8 9 end process; 10 end architecture;

We will now go through the simulation of the architecture's process step-by-step, using the process simulation logic shown in the flow-chart.

#### **Example: Process Simulation** HWMod **WS24** fetch $1^{st}$ statement 1 architecture beh of abc is Example execute wait for yes signal a, b, c : boolean; 2 ves registered is wait? next event 3 begin statements process 4 no no 5 begin wait trig b <= a; 6 is end of gered? 7 c <= b; process? 8 wait on a, b; yes 9 end process; no fetch next register 10 end architecture; statement statement

We assume that all signals are initially false and that the process is executed for the first time. Note that we will keep track of the current values of all signals in the highlighted area below the flow chart.

## Example: Process Simulation

HWMod WS24

Beh. Mod. Introduction Sensitivity Process Simulation Example Observations Variables Remarks

```

1 architecture beh of abc is

signal a, b, c : boolean;

2

3 begin

4

process

5

begin

b <= a;

6

c <= b;

7

wait on a, b;

8

9

end process;

10 end architecture;

```

Our example starts with an assumed transition of signal a from false to true. The simulator knows that the process is sensitive to a and thus that it is to be executed.

## Example: Process Simulation

#### HWMod WS24

Beh. Mod. Introduction Sensitivity Process Simulatio Example Observations Variables Remarks

```

1 architecture beh of abc is

signal a, b, c : boolean;

2

3 begin

4

process

5

begin

b <= a;

6

c <= b;

7

wait on a, b;

8

9

end process;

10 end architecture;

```

Input a changes

In a first step, the simulator will fetch the first statement of the process body. In our case that's the assignment of a to b. Note that we highlight the current statement, as well as the current part of the flowchart we consider.

## **Example: Process Simulation**

Beh. Mod. Introduction Sensitivity Process Simulatio Example Observations Variables Remarks

a: true

b: false

C: false

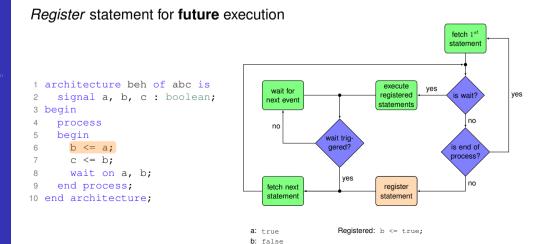

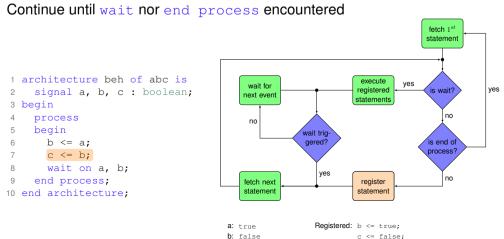

Next, based on the fetched statement the simulator has to decide how to proceed. Since the statement is a signal assignment, and thus neither a wait statement nor the end of the process, it will continue to the *register statement* tate.

## Example: Process Simulation

#### HWMod WS24

Beh. Mod. Introduction Sensitivity Process Simulatio Example Observations Variables Remarks

a: true

b: false

In this state, the simulator will store the fetched statement for *future* xecution. It must be stressed that the assignment does **not take place immediately**. As we will see later, this is required to mimic the concurrent execution of a process.

## **Example: Process Simulation**

Beh. Mod. Introduction Sensitivity Process Simulatio Example Observations Variables Remarks

C: false

Note that we will track all registered statements below the flowchart.

## Example: Process Simulation

Register statement for future execution

HWMod

**WS24**

```

1 architecture beh of abc is

signal a, b, c : boolean;

2

3 begin

4

process

5

begin

b <= a;

6

c <= b;

7

wait on a, b;

8

9

end process;

10 end architecture;

```

After its registration, the simulator is for now done with this statement and thus continues by fetching the next one. This is the assignment of b to c.

## **Example: Process Simulation**

#### HWMod WS24

Beh. Mod. Introduction Sensitivity Process Simulatio Example Observations Variables Remarks

```

1 architecture beh of abc is

signal a, b, c : boolean;

2

3 begin

4

process

5

begin

b <= a;

6

7

c <= b;

wait on a, b;

8

9

end process;

10 end architecture;

```

Fetch the next statement

Registered: b <= true;

This brings us back to where we started with the first statement where the simulator will again check if the fetched statement is either a wait statement or the end of the process.

## **Example: Process Simulation**

Beh. Mod. Introduction Sensitivity Process Simulation Example Observations Variables Remarks

9

However, since the statement in line 7 is neither, the simulator once again continues by registering the statement without actually performing the assignment. Note how the value of b is still false because the previous assignment to b was not yet executed.

## **Example: Process Simulation**

Example

C: false

The simulator then continues by fetching the next statement, which is wait on.

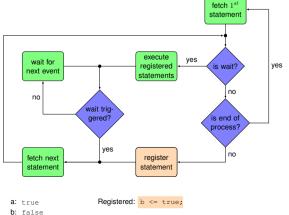

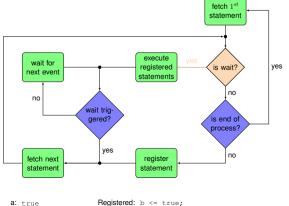

#### **Example: Process Simulation** HWMod Continue until wait nor end process encountered **WS24** fetch 1st statement 1 architecture beh of abc is Example execute yes wait for ves registered is wait? signal a, b, c : boolean; 2 next event statements 3 begin no 4 process no 5 begin wait trig b <= a; gered? is end of 6 process? c <= b; 7 wait on a, b; 8 yes no end process; register 9 fetch next 10 end architecture; statement statement Registered: b <= true; a: true

b: false

C: false

c <= false;

With this statement being a wait statement, the simulation of the process transitions to the state where the registered statements are executed.

## **Example: Process Simulation**

#### HWMod WS24

Beh. Mod. Introduction Sensitivity Process Simulation Example Observations Variables Remarks

```

1 architecture beh of abc is

signal a, b, c : boolean;

2

3 begin

4

process

5

begin

b <= a;

6

c <= b;

7

wait on a, b;

8

9

end process;

10 end architecture;

```

wait statement encountered

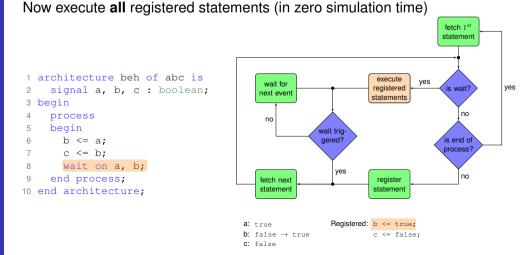

First, the registered assignment of a to b is executed. Since a was true during the registration, b will become true as well.

## **Example: Process Simulation**

Beh. Mod. Introduction Sensitivity Process Simulatio Example Observations Variables Remarks

Then, the second registered statement will be executed. This is the assignment of b to c. However, as b was false when this assignment got registered, c keeps its value of false.

## **Example: Process Simulation**

Beh. Mod. Introduction Sensitivity Process Simulatio Example Observations Variables Remarks

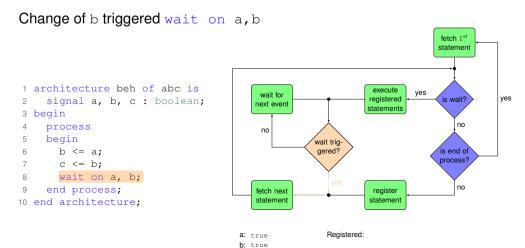

Next, the simulator checks if the execution of the registered assignments has triggered the currently fetched wait statement. In this case it is thus checked whether b is on the sensitivity list.

## Example: Process Simulation

Beh. Mod. Introduction Sensitivity Process Simulatio Example Observations Variables Remarks

C: false

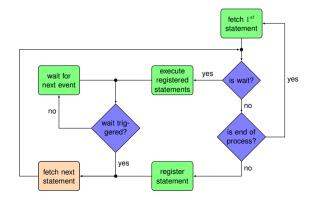

Since this is the case, the next statement is fetched and the process is simulated again with the changed values.

## **Example: Process Simulation**

#### HWMod **WS24**

Example

```

1 architecture beh of abc is

signal a, b, c : boolean;

2

3 begin

4

process

5

begin

b <= a;

6

c <= b;

7

wait on a, b;

8

9

end process;

10 end architecture;

```

Fetch next statement

### -Behavioral Modeling

Process Simulation

### **Example: Process Simulation**

## **Example: Process Simulation**

#### HWMod **WS24**

Example

```

1 architecture beh of abc is

signal a, b, c : boolean;

2

3 begin

4

process

5

begin

6

b <= a;

7

c <= b;

wait on a, b;

8

9

end process;

10 end architecture;

```

End of process  $\Rightarrow$  Repeat

Registered:

b: true C: false

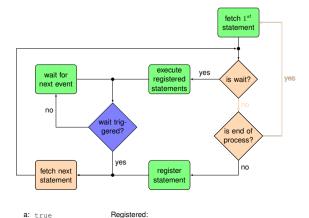

### -Behavioral Modeling └─Process Simulation └─**Observations: Process Simulation**

statements are not executed immediately, but rather gathered until a wait is noountered. Then they are all executed without consuming simulation time his mimics a concurrent execution.

Let us take a moment to express some observations we were able make during the example process simulation we just saw.

## **Observations: Process Simulation**

#### HWMod WS24

Seh. Mod. Introduction Sensitivity Process Simulation Example Observations Variables Remarks

### Observation I

Statements are not executed immediately, but rather gathered until a wait is encountered. Then they are all executed without consuming simulation time. This mimics a concurrent execution.

## ─Behavioral Modeling └─Process Simulation └─Observations: Process Simulation

Statements are not executed immediately, but rather gathered until a wait encountered. Then they are all executed without consuming simulation tim This mimics a concurrent execution.

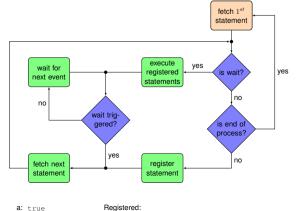

Without b in the sensitivity list in the example, c would end remaining false until the next change of  $a \Rightarrow$  proper sensitivity list paramount.

The first thing we could notice was that statements are not executed immediately but rather *registered* or future execution. Only when some wait statement is encountered, the registered statements get executed. Admittedly, this seems quite strange. So why is that? Well, the thing is that a process must ultimately be capable to describe a concurrent circuit. Such a circuit does not operate sequentially as suggested by the process. However, the primary problem of a sequential description are actually side effects. Not executing signal assignments mitigates such side effects, as the states of all signals throughout the process execution will only change at the simulation time and thus seemingly concurrent to another. Next, as motivated before, a proper sensitivity list is paramount. We could observe that during this example. If b was not on the sensitivity list the process would have become suspended after encountering the wait on statement for the first time, leading to a behavior that will most likely strongly deviate from the one the designer had in mind.

## **Observations: Process Simulation**

#### HWMod WS24

Seh. Mod. Introduction Sensitivity Process Simulation Example Observations Variables Remarks

### **Observation I**

Statements are not executed immediately, but rather gathered until a wait is encountered. Then they are all executed without consuming simulation time. This mimics a concurrent execution.

### **Observation II**

Without b in the sensitivity list in the example, c would end remaining false until the next change of  $a \Rightarrow$  proper sensitivity list paramount.

## ─Behavioral Modeling └─Process Simulation └─Observations: Process Simulation

$\label{eq:constraint} \begin{array}{l} \hline \textbf{Constraint} \\ \textbf{Constraint} \\$

Finally, looking at the flowchart and knowing what every node inside it means clearly tells us that a process without a wait statement will loop endlessly. Keep that in mind, as wait statements are something beginners tend to forget.

## **Observations: Process Simulation**

#### HWMod WS24

Seh. Mod. Introduction Sensitivity Process Simulation Example Observations Variables Remarks

### **Observation I**

Statements are not executed immediately, but rather gathered until a wait is encountered. Then they are all executed without consuming simulation time. This mimics a concurrent execution.

### **Observation II**

Without b in the sensitivity list in the example, c would end remaining <code>false</code> until the next change of  $a \Rightarrow$  proper sensitivity list paramount.

### **Observation III**

A process without (implicit) wait statement loops endlessly.

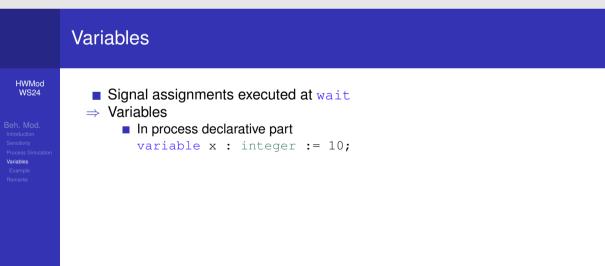

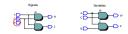

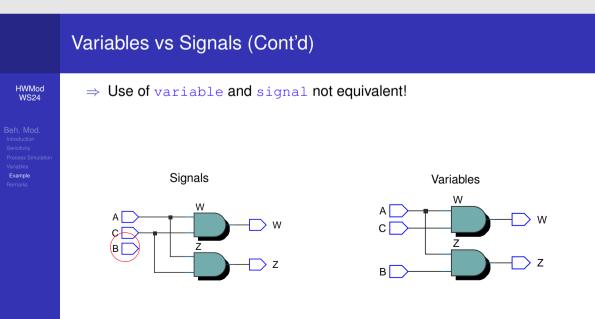

### -Behavioral Modeling └─Variables └─**Variables**

Signal assignments executed at wait

During the previous few slides we could observe that signal assignments only take an effect at wait statements. However, sometimes we would like an assignment to behave like the ones we are familiar with from typical software programming.

## Variables

HWMod WS24

Beh. Mod. Introduction Sensitivity Process Simulati Variables Example Remarks Signal assignments executed at wait

### └─Behavioral Modeling └─Variables └**─Variables**

Signal assignments executed at wait

Variables

This is why VHDL also comes with variables in addition to signals.

# HWMod WS24 Signal assignments executed at wait Variables Variables Variables

### --Behavioral Modeling └--Variables └--**Variables**

Such variables can be declared in the declarative parts of processes and some other VHDL constructs, but not within architectures. As shown by the example on the slide, syntactically a variable declaration is, except for the variable keyword, equivalent to a signal declaration.

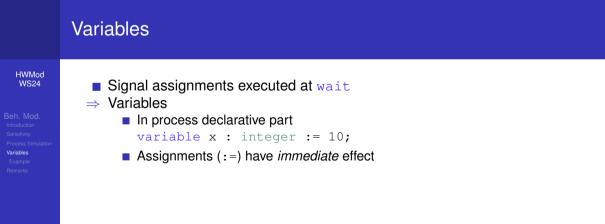

As alread foreshadowed, the key difference between variables and signals is that assignments to variables happen *immediately*

#### -Behavioral Modeling └─Variables └─**Variables**

Signal assignments executed at weit Variables In process declarative part variable x : integer := 10; Assignments (:=) have immediate effect Not in sensitive list

Furthermore, variables can never be on the sensitivity list of a process. If we recall that the elements of the sensitivity list do to some extent correspond to the inputs of the sub-circuit described by the process, this makes sense as variables are declared within a process and thus cannot act as inputs to the respective circuit.

# HWMdd WS24 Br. Mod Wradwar Yenews Br. Mod Wradwar Yenews Image: Signal assignments executed at wait > Variables Image: Ima

#### -Behavioral Modeling └─Variables └─**Variables**

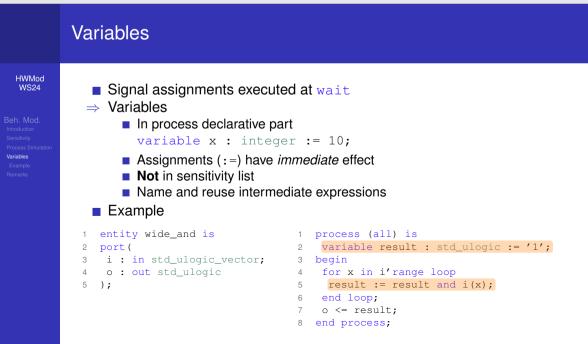

Signal assignments executed at wait Variables In process declarative part variable x : integer := 10; Assignments (:-) have immediate effect Not in sensitivity list Name and reuse intermediate expressions

In general, variables allows referring to intermediate expressions and results throughout a process body, thus allowing to reuse such values. Variables can thus lead to concise and maintainable code.

# Signal assignments executed at wait Structure Your and Process declarative part variable x : integer := 10; Assignments (:=) have immediate effect Not in sensitivity list Name and reuse intermediate expressions

—Behavioral Modeling └─Variables └─**Variables**

This is illustrated by the example of a wide AND gate which determines the bitwise AND of the elements of a vector.

#### Variables HWMod Signal assignments executed at wait **WS24** $\Rightarrow$ Variables In process declarative part variable x : integer := 10; Variables Assignments (:=) have immediate effect Not in sensitivity list Name and reuse intermediate expressions Example 1 entity wide\_and is 1 process (all) is 2 port( 2 variable result : std\_ulogic := '1'; 3 i : in std\_ulogic\_vector; 3 begin o : out std\_ulogic 4 for x in i'range loop 4 5 result := result and i(x); 5 ); 6 end loop; 7 o <= result;</pre> 8 end process;

In the example we declare a variable result holds the intermediate results of a loop that ANDs all elements of the given input vector.

Let us now consider an example to highlight the difference between variables and signals in processes. While the example is a bit constructed, it is very illustrative.

# Example: Variables vs Signals

HWMod WS24

3eh. Mod. Introduction Sensitivity Process Simulatio Variables Example Remarks

Consider the process that combines the entity inputs q, b and c to drive two internal signals w and z. Note that we have ommitted the entity declaration here as it is not vital to the example. The signals x and y will be used to store intermediate values.

## Example: Variables vs Signals

```

HWMod

WS24

```

```

Example

```

| 1  | architecture sig of app is                 |

|----|--------------------------------------------|

| 2  | <pre>signal w, x, y, z : std_ulogic;</pre> |

| 3  | begin                                      |

| 4  | process (all) begin                        |

| 5  | x <= a;                                    |

| 6  | y <= b;                                    |

| 7  | z <= x and y;                              |

| 8  | у <= с;                                    |

| 9  | w <= x and y;                              |

| 10 | end process;                               |

| 11 | end architecture;                          |

$\label{eq:constraints of the state of the second second$

Initially, all signals are assumed to be high, with  $_{\rm C}$  transitioning to low. The process is assumed to have been suspended before.

## Example: Variables vs Signals

```

HWMod

WS24

```

Beh. Mod. Introduction Sensitivity Process Simulati Variables Example Remarks

```

1 architecture sig of app is

2 signal w, x, y, z : std_ulogic;

3 begin

4 process (all) begin

5 x <= a;

6 y <= b;

7 z <= x and y;

8 y <= c;

9 w <= x and y;

10 end process;

11 end architecture;</pre>

```

$\label{eq:constraints} \begin{array}{c} 1 \quad \text{arealistications} \quad \text{eff} \quad \text{of app is} \\ 1 \quad \text{arealistic} \quad \text{eff} \quad \text{arealistic} \\ 2 \quad \text{begins} \quad \\ 1 \quad \text{eff} \quad \text{begins} \quad \\ 2 \quad \text{eff} \quad \\ 2 \quad \text{eff} \quad \text{begins} \quad \\ 2 \quad \text{eff} \quad \\ 2 \quad$

As the process uses the all keyword in its sensitivity list, and reads c, the transition of this signal will lead to its execution. You can now simply apply what you learned about the semantics of signal assignments in processes to determine the values of the architecture's four signals after the process execution.

## Example: Variables vs Signals

```

HWMod

WS24

```

Beh. Mod. Introduction Sensitivity Process Simulati Variables Example Remarks

```

1 architecture sig of app is

signal w, x, y, z : std_ulogic;

2

3 begin

4 process (all) begin

5 x <= a;

6

y <= b;

7

z \leq x and y;

8

y <= c;

w \leq x and y;

9

end process;

10

11 end architecture;

```

First, a will be assigned to x, which will thus be set to '1'. However, note that we do not explicitly keep track of registered statements, but rather let later assignments override previous ones. This will become clear shortly.

## Example: Variables vs Signals

```

HWMod

WS24

```

Beh. Mod. Introduction Sensitivity Process Simulati Variables Example Remarks

| 1 architecture sig of app is                 |

|----------------------------------------------|

| <pre>2 signal w, x, y, z : std_ulogic;</pre> |

| 3 begin                                      |

| 4 process (all) begin                        |

| 5 x <= a;                                    |

| 6 y <= b;                                    |

| 7 $z \leq x$ and y;                          |

| 8 y <= c;                                    |

| 9 $w \leq x$ and y;                          |

| 10 end process;                              |

| 11 end architecture;                         |

| Iteration # | signal values at end |

|-------------|----------------------|

| 1           | x='1'                |

| 2           |                      |

ial Values: x-u-c-u-x-x-z-1\*, c-\*1\*→\*) Iteration # signal values at end 1 ×\*\*1\*, y=\*1\*

Next, b and thus '1' is assigned to y.

# Example: Variables vs Signals

```

HWMod

WS24

```

Beh. Mod. Introduction Sensitivity Process Simulati Variables Example Remarks

| 1  | architecture sig of app is                 |

|----|--------------------------------------------|

| 2  | <pre>signal w, x, y, z : std_ulogic;</pre> |

| 3  | begin                                      |

| 4  | process (all) begin                        |

| 5  | x <= a;                                    |

| 6  | y <= b;                                    |

| 7  | $z \leq x$ and $y$ ;                       |

| 8  | у <= с;                                    |

| 9  | w <= x and y;                              |

| 10 | end process;                               |

| 11 | end architecture;                          |

| Iteration # | signal values at end |

|-------------|----------------------|

| 1           | x='1', y='1'         |

| 2           |                      |

1 stricted use sig of app is 2 signal w, w, y, z : sta\_ulogi 3 begin 4 process (all) begin 5  $X < a_0$ 7  $X < a_0$ 7  $X < a_0$ 7  $X < a_0$ 8  $X < a_0$ 9  $X < a_0$

Then, z is set to the logical AND of x and y.

## Example: Variables vs Signals

HWMod WS24

Beh. Mod. Introduction Sensitivity Process Simulati Variables Example Remarks

| 1  | architecture sig of app is                 |

|----|--------------------------------------------|

| 2  | <pre>signal w, x, y, z : std_ulogic;</pre> |

| 3  | begin                                      |

| 4  | process (all) begin                        |

| 5  | x <= a;                                    |

| 6  | y <= b;                                    |

| 7  | $z \leq x$ and $y;$                        |

| 8  | у <= с;                                    |

| 9  | w <= x and y;                              |

| 10 | end process;                               |

| 11 | end architecture;                          |

| Iteration # | signal values at end  |

|-------------|-----------------------|

| 1           | x='1', y='1'<br>z='1' |

| 2           |                       |

Now something interesting happens. c is assigned to y, overriding the previous assignment to y.

## Example: Variables vs Signals

```

HWMod

WS24

```

Beh. Mod. Introduction Sensitivity Process Simulation Variables Example Remarks

| 1 architecture sig of app is   |     |

|--------------------------------|-----|

| 2 signal w, x, y, z : std_ulog | ic; |

| 3 begin                        |     |

| 4 process (all) begin          |     |

| 5 x <= a;                      |     |

| 6 y <= b;                      |     |

| 7 $z \leq x$ and y;            |     |

| 8 y <= c;                      |     |

| 9 $w \leq x$ and y;            |     |

| 10 end process;                |     |

| 11 end architecture;           |     |

| Iteration # | signal values at end  |

|-------------|-----------------------|

| 1           | x='1', y='0'<br>z='1' |

| 2           |                       |

$\label{eq:constraints} \begin{array}{c} \begin{array}{l} \mbox{traints} \\ \mbox$

Finally, w is assigned the logical AND of x and y. Note that since the assignments have not yet taken place as there was no wait statement, w will become '1'. Now, since the process is sensitive to y, which changed its value, the process will trigger again.

# Example: Variables vs Signals

```

HWMod

WS24

```

Seh. Mod. Introduction Sensitivity Process Simulatin Variables Example Remarks

| 1 architecture sig of app is                 |

|----------------------------------------------|

| <pre>2 signal w, x, y, z : std_ulogic;</pre> |

| 3 begin                                      |

| 4 process (all) begin                        |

| 5 x <= a;                                    |

| 6 y <= b;                                    |

| 7 $z \leq x$ and y;                          |

| 8 y <= c;                                    |

| 9 $w \leq x$ and y;                          |

| 10 end process;                              |

| <pre>11 end architecture;</pre>              |

|                                              |

| Iteration # | signal values at end         |

|-------------|------------------------------|

| 1           | x='1', y='0'<br>z='1', w='1' |

| 2           |                              |

The values of the signals after this second iteration are shown on the slide. In case you have doubts about some values, you can simply determine them step-by-step as we did in the first iteration. Since none of the signals to which the process is sensitive to changed in this second iteration, the process will again be suspended.

## Example: Variables vs Signals

```

HWMod

WS24

```

Beh. Mod. Introduction Sensitivity Process Simulati Variables Example Remarks

| 1  | architecture sig of app is                 |

|----|--------------------------------------------|

| 2  | <pre>signal w, x, y, z : std_ulogic;</pre> |

| 3  | begin                                      |

| 4  | process (all) begin                        |

| 5  | x <= a;                                    |

| 6  | y <= b;                                    |

| 7  | z <= x and y;                              |

| 8  | у <= с;                                    |

| 9  | w <= x and y;                              |

| 10 | end process;                               |

| 11 | end architecture;                          |

| Iteration # | signal values at end         |

|-------------|------------------------------|

| 1           | x='1', y='0'<br>z='1', w='1' |

| 1           | z='1', w='1'                 |

| 9           | w='0', x='1'<br>y='0', z='0' |

| 2           | y='0', z='0'                 |

Let us now move our attention to a slightly modified version of this process.

## Example: Variables vs Signals

HWMod WS24

Beh. Mod. Introduction Sensitivity Process Simulatio Variables Example Remarks

```

1 architecture sig of app is

signal w, x, y, z : std_ulogic;

2

3 begin

4 process (all) begin

5 x <= a;

6

y <= b;

7

z \leq x and y;

y <= c;

8

w \leq x and y;

9

end process;

10

11 end architecture;

```

```

1 architecture var of app is

signal w, z : std_ulogic;

2

3 begin

4

process (all) is

5

variable x, y : std_ulogic;

6

begin

7

x := a;

8

y := b;

9

z \leq x \text{ and } y;

y := c;

10

11

w \leq x and y;

end process;

12

13 end architecture;

```

| Iteration # | signal values at end         |

|-------------|------------------------------|

| 1           | x='1', y='0'<br>z='1', w='1' |

| 2           | w='0', x='1'<br>y='0', z='0' |

Instead of signals for the intermediate values x and y, corresponding variables are declared and used within the process.

## Example: Variables vs Signals

HWMod WS24

Beh. Mod. Introduction Sensitivity Process Simulatio Variables Example Remarks

```

1 architecture sig of app is

signal w, x, y, z : std_ulogic;

2

3 begin

process (all) begin

4

5

x <= a;

y <= b;

6

7

z \leq x and y;

y <= c;

8

w \leq x and y;

9

end process;

10

11 end architecture;

```

```

1 architecture var of app is

signal w, z : std_ulogic;

2

3 begin

4

process (all) is

5

variable x, y : std_ulogic;

6

begin

7

x := a;

8

y := b;

9

z \leq x \text{ and } y;

y := c;

10

11

w \leq x \text{ and } y;

end process;

12

13 end architecture;

```

| Iteration # | signal values at end         |

|-------------|------------------------------|

| 1           | x='1', y='0'<br>z='1', w='1' |

| 2           | w='0', x='1'<br>y='0', z='0' |

| ues at en |

|-----------|

| ues at en |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

| id_ulogi  |

|           |

|           |

| 00104     |

|           |

As before, let us now consider the effects the statements inside the process body have on the signals step-by-step.

## Example: Variables vs Signals

HWMod WS24

Beh. Mod. Introduction Sensitivity Process Simulatio Variables Example Remarks

```

1 architecture sig of app is

signal w, x, y, z : std_ulogic;

2

3 begin

4 process (all) begin

5 x <= a;

6

y <= b;

7

z \leq x and y;

y <= c;

8

w \leq x and y;

9

10 end process;

11 end architecture;

```

```

1 architecture var of app is

signal w, z : std_ulogic;

2

3 begin

4

process (all) is

5

variable x, y : std_ulogic;

6

begin

7

x := a;

8

y := b;

9

z \leq x and y;

y := c;

10

11

w \ll x and y;

end process;

12

13 end architecture;

```

| Iteration # | signal values at end         |   | Iteration # | signal values at end |    |

|-------------|------------------------------|---|-------------|----------------------|----|

| 1           | x='1', y='0'<br>z='1', w='1' | - | 1           |                      |    |

| 2           | w='0', x='1'<br>y='0', z='0' | - | 2           |                      | 12 |

| 2                                  | w="0", x="1"<br>y="0", z="0" | _     | 2                   |                     |

|------------------------------------|------------------------------|-------|---------------------|---------------------|

| 1                                  | x='1', y='0'                 |       | 1                   | x='1', y='1'        |

| Iteration #                        | signal values at end         | _     | Iteration #         | signal values at er |

| Initial Values: A-II-C             | -N-X-X-X-1", C-"1"-+"        |       |                     |                     |

|                                    |                              | 13 04 | d architer          | ture;               |

|                                    |                              |       | end proces          |                     |

| 10 end process<br>11 end architect |                              |       | y 1- 0j<br>u <- x A |                     |

| 0 ¥ <= x M                         |                              |       | 2 (+ X A            | -4 77               |

| 1 V ST 01                          | · 21                         |       | V 1- bi             |                     |

| a y <- by<br>7 z <- x M            |                              |       | k i- Ai             |                     |

| 5 X <= 34                          |                              |       |                     | H, Y : std_plog     |

| 4 BECCESS [A]                      | 13 beain                     |       | DECOMPAGE EN        | 115 14              |

| z signal w, s<br>z besin           | , y, z : std_plogic;         |       | signal w,           | a : std_ulogic;     |

|                                    | sig of app is                |       |                     | var of app is       |

First, the two variables x and y are assigned a respectively b. Since variable assignments take place immediately, both variables will from now on hold the value '1'.

## Example: Variables vs Signals

HWMod WS24

3eh. Mod. Introduction Sensitivity Process Simulatio Variables Example Remarks

```

1 architecture sig of app is

signal w, x, y, z : std_ulogic;

2

3 begin

4 process (all) begin

5 x <= a;

y <= b;

6

7

z \leq x and y;

8

y <= c;

w \leq x and y;

9

end process;

10

11 end architecture;

```

```

1 architecture var of app is

signal w, z : std_ulogic;

2

3 begin

4

process (all) is

5

variable x, y : std_ulogic;

6

begin

7

x := a;

8

y := b;

9

z \leq x and y;

y := c;

10

11

w \leq x \text{ and } y;

end process;

12

13 end architecture;

```

| Iteration # | signal values at end         | Iteration # | signal values at end |

|-------------|------------------------------|-------------|----------------------|

| 1           | x='1', y='0'<br>z='1', w='1' | 1           | x='1', y='1'         |

| 2           | w='0', x='1'<br>y='0', z='0' | 2           |                      |

| 11 end |  | 11<br>12<br>13 | y i= oj<br>u <= x J<br>end proces<br>end architer |  |

|--------|--|----------------|---------------------------------------------------|--|

|        |  |                |                                                   |  |

As before, z is now assigned the value '1' as both operands of the AND are high.

## Example: Variables vs Signals

HWMod WS24

Beh. Mod. Introduction Sensitivity Process Simulatio Variables Example Remarks

```

1 architecture sig of app is

signal w, x, y, z : std_ulogic;

2

3 begin

4 process (all) begin

5 x <= a;

6

y <= b;

7

z \leq x and y;

8

y <= c;

w \leq x and y;

9

10 end process;

11 end architecture;

```

```

1 architecture var of app is

signal w, z : std_ulogic;

2

3 begin

4

process (all) is

5

variable x, y : std_ulogic;

6

begin

7

x := a;

8

y := b;

9

z \leq x and y;

10

y := c;

11

w \leq x \text{ and } y;

end process;

12

13 end architecture;

```

12

| Iteration # | signal values at end         | Iteration # | signal values at end  |

|-------------|------------------------------|-------------|-----------------------|

| 1           | x='1', y='0'<br>z='1', w='1' | 1           | x='1', y='1'<br>z='1' |

| 2           | w='0', x='1'<br>y='0', z='0' | 2           |                       |

|      | 2                   | w="0", x="1"<br>v="0", z="0" | -  | 2            | 27.1                             |

|------|---------------------|------------------------------|----|--------------|----------------------------------|

|      | 1                   | x='1', y='0'                 |    | 1            | x='1', y='0'                     |

|      | Iteration #         | signal values at end         |    | Iteration #  | signal values at en              |

| Init | al Values: x-s-c    | -N-X-X-X-1', C-'1'-+'        | 0* |              |                                  |

|      |                     |                              | 13 | end archites | cure;                            |

|      |                     |                              |    | end proces   |                                  |

|      | end architect       |                              |    | N 57 X 4     | ad va                            |

|      | end process         |                              |    | V 1- 01      | 11                               |

|      | y <- cy<br>w <- x N |                              |    | y i= bj      |                                  |

|      | 2 <= × N            | 54 Y)                        |    |              |                                  |

|      | $y \leftarrow by$   |                              |    | begin        |                                  |

|      | x <= ay             |                              |    |              | x, y : std_ulogi                 |

|      | process (A          | 11 bests                     |    | DECOMPAGE EA | 111 14                           |

|      | beain               | s, y, a r stallarsdard       |    | begin        | a i sea arageo)                  |

|      |                     | sig of app is                |    |              | var of app is<br>z : std_ulogic; |

Now the variable y is aassigned the value of c. Since this assignment takes place immediately, and since c is ' 0', y will from now on be low. This is in contrast to before we y was ' 1' during the whole process execution since the signal assignments were only registered but did not take place until the final implicit wait on statement.

## Example: Variables vs Signals

```

HWMod

WS24

```

3eh. Mod. Introduction Sensitivity Process Simulatio Variables Example Remarks

```

1 architecture sig of app is

signal w, x, y, z : std_ulogic;

2

3 begin

4 process (all) begin

5

x <= a;

6

y <= b;

7

z \leq x and y;

y <= c;

8

w \leq x and y;

9

end process;

10

11 end architecture;

```

```

1 architecture var of app is

signal w, z : std_ulogic;

2

3 begin

process (all) is

4

5

variable x, y : std_ulogic;

6

begin

7

x := a;

8

y := b;

9

z \leq x \text{ and } y;

10

y := c;

11

w \leq x \text{ and } y;

12

end process;

13 end architecture;

```

| Iteration # | signal values at end         | Iteration # | signal values at end  |

|-------------|------------------------------|-------------|-----------------------|

| 1           | x='1', y='0'<br>z='1', w='1' | 1           | x='1', y='0'<br>z='1' |

| 2           | w='0', x='1'<br>y='0', z='0' | 2           |                       |

| s w <- x And y;     s z <- x And y;     s add y;     s z <- x and y;     s add y;     s z <- x and y;     z <- z and y;           |         |