# Hardware Modeling [VU] (191.011)

## – WS25 –

### Behavioral Modeling

Florian Huemer & Sebastian Wiedemann & Dylan Baumann

WS 2025/26

# Introduction

HWMOD

WS25

Beh. Mod.

Introduction

About

Example

Sensitivity

Process Simulation

Variables

Remarks

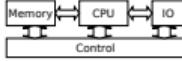

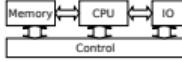

## Concurrent assignments and structural modeling

- Can model all **combinational** hardware

- Hardly scales...

|                               | Behavior                                                                      | Structure                                                                          | Geometry                                                                            |

|-------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| System Level                  | Inputs : Keyboard<br>Output: Display<br>Function: .....                       |  |  |

| Algorithmic Level             | while input<br>read English text<br>translate to German<br>output German Text |  |  |

| Register Transfer Level (RTL) | if A='1' then<br>B:= B+1<br>else<br>B:= B<br>end if                           |  |  |

| Logic Level                   | D = NOT E<br>C = (D OR B) AND A                                               |  |  |

| Circuit Level                 | $\frac{dU}{dt} = R \frac{dI}{dt} + \frac{1}{C} + L \frac{d^2I}{dt^2}$         |  |  |

# Introduction

HWMod

WS25

Beh. Mod.

Introduction

About

Example

Sensitivity

Process Simulation

Variables

Remarks

- Concurrent assignments and structural modeling

- Can model all **combinational** hardware

- Hardly scales...**how?**

|                               | Behavior                                                                      | Structure                                                                          | Geometry                                                                            |

|-------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

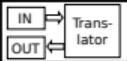

| System Level                  | Inputs : Keyboard<br>Output: Display<br>Function: .....                       |  |  |

| Algorithmic Level             | while input<br>read English text<br>translate to German<br>output German Text |  |  |

| Register Transfer Level (RTL) | if A='1' then<br>B:=1<br>else<br>B:=B<br>end if                               |  |  |

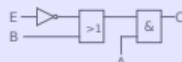

| Logic Level                   | D = NOT E<br>C = (D OR B) AND A                                               |  |  |

| Circuit Level                 | $\frac{dU}{dt} = R \frac{dI}{dt} + \frac{1}{C} + L \frac{d^2I}{dt^2}$         |  |  |

# Introduction

HWMod

WS25

Beh. Mod.

Introduction

About

Example

Sensitivity

Process Simulation

Variables

Remarks

- Concurrent assignments and structural modeling

- Can model all **combinational** hardware

- Hardly scales...**how?**

⇒ *Behavioral Modeling*

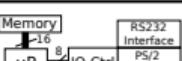

|                               | Behavior                                                                      | Structure                                                                          | Geometry                                                                            |

|-------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| System Level                  | Inputs : Keyboard<br>Output: Display<br>Function: .....                       |  |  |

| Algorithmic Level             | while input<br>read English text<br>translate to German<br>output German Text |  |  |

| Register Transfer Level (RTL) | if A='1' then<br>B:= B+1<br>else<br>B:= B                                     |  |  |

| Logic Level                   | Modeling<br>$C = (D \text{ OR } B) \text{ AND } A$                            |  |  |

| Circuit Level                 | $\frac{dU}{dt} = R \frac{dI}{dt} + \frac{1}{C} + L \frac{d^2I}{dt^2}$         |  |  |

# Behavioral Modeling

HWMod

WS25

Beh. Mod.

Introduction

About

Example

Sensitivity

Process Simulation

Variables

Remarks

- Revolves around processes

- Must be synthesizable

# Behavioral Modeling

HWMod

WS25

Beh. Mod.

Introduction

About

Example

Sensitivity

Process Simulation

Variables

Remarks

- Revolves around processes

- Must be synthesizable

- “single-use entity and architecture”

# Behavioral Modeling

HWMod

WS25

Beh. Mod.

Introduction

About

Example

Sensitivity

Process Simulation

Variables

Remarks

- Revolves around processes

- Must be synthesizable

- “single-use entity and architecture”

- Control flow statements and *variables*

- *Sequential* description

# Behavioral Modeling

HWMOD

WS25

Beh. Mod.

Introduction

About

Example

Sensitivity

Process Simulation

Variables

Remarks

- Revolves around processes

- Must be synthesizable

- “single-use entity and architecture”

- Control flow statements and *variables*

- *Sequential* description

- **Complements** struct. modeling and concurrent assignments

# Behavioral Modeling

HWMOD

WS25

Beh. Mod.

Introduction

About

Example

Sensitivity

Process Simulation

Variables

Remarks

- Revolves around processes

- Must be synthesizable

- “single-use entity and architecture”

- Control flow statements and *variables*

- *Sequential* description

- **Complements** struct. modeling and concurrent assignments

- Ubiquitous in synchronous designs

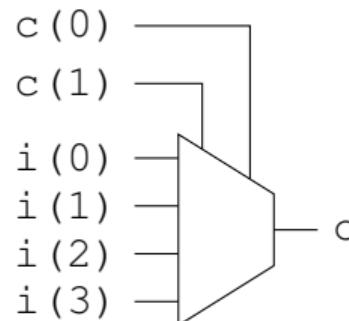

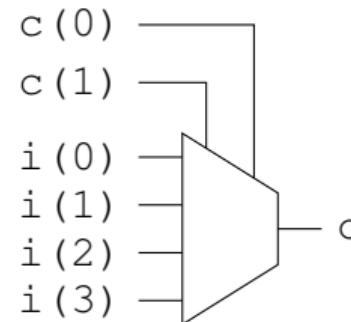

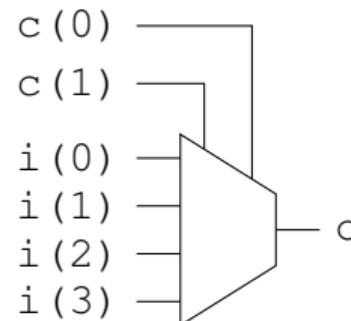

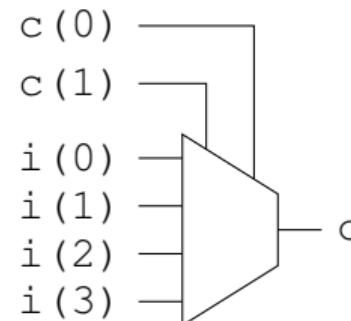

# Example: Multiplexer

HWMod

WS25

Beh. Mod.

Introduction

About

Example

Sensitivity

Process Simulation

Variables

Remarks

```

4 entity mux_41 is

5   port (

6     c : in  std_ulogic_vector(1 downto 0);

7     i : in  std_ulogic_vector(3 downto 0);

8     o : out std_ulogic

9   );

10 end entity;

```

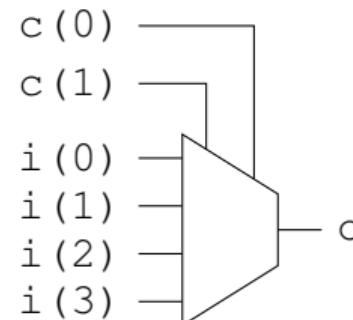

# Example: Multiplexer

HWMod

WS25

Beh. Mod.

Introduction

About

Example

Sensitivity

Process Simulation

Variables

Remarks

```

4 entity mux_41 is

5   port (

6     c : in  std_ulogic_vector(1 downto 0);

7     i : in  std_ulogic_vector(3 downto 0);

8     o : out std_ulogic

9   );

10 end entity;

12 architecture csa of mux_41 is

13 begin

14   o <= i(0) when not c(1) and not c(0) else

15     i(1) when not c(1) and      c(0) else

16     i(2) when      c(1) and not c(0) else

17     i(3) when      c(1) and      c(0);

18 end architecture;

```

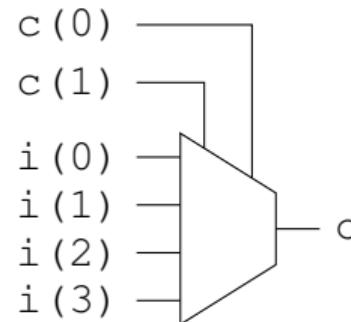

# Example: Multiplexer

HWMod

WS25

Beh. Mod.

Introduction

About

Example

Sensitivity

Process Simulation

Variables

Remarks

```

4 entity mux_41 is

5   port (

6     c : in  std_ulogic_vector(1 downto 0);

7     i : in  std_ulogic_vector(3 downto 0);

8     o : out std_ulogic

9   );

10 end entity;

12 architecture beh of mux_41 is

13 begin

14   process begin

15     case c is

16       when '0' & '0' => o <= i(0);

17       when '0' & '1' => o <= i(1);

18       when '1' & '0' => o <= i(2);

19       when '1' & '1' => o <= i(3);

20       when others      => null;

21     end case;

22     wait;

23   end process;

24 end architecture;

```

# Example: Multiplexer

HWMod

WS25

Beh. Mod.

Introduction

About

Example

Sensitivity

Process Simulation

Variables

Remarks

```

4 entity mux_41 is

5   port (

6     c : in  std_ulogic_vector(1 downto 0);

7     i : in  std_ulogic_vector(3 downto 0);

8     o : out std_ulogic

9   );

10 end entity;

12 architecture beh of mux_41 is

13 begin

14   process begin

15     case c is

16       when '0' & '0' => o <= i(0);

17       when '0' & '1' => o <= i(1);

18       when '1' & '0' => o <= i(2);

19       when '1' & '1' => o <= i(3);

20       when others      => null;

21     end case;

22     wait;

23   end process;

24 end architecture;

```

# Example: Multiplexer

HWMod

WS25

Beh. Mod.

Introduction

About

Example

Sensitivity

Process Simulation

Variables

Remarks

```

4 entity mux_41 is

5   port (

6     c : in  std_ulogic_vector(1 downto 0);

7     i : in  std_ulogic_vector(3 downto 0);

8     o : out std_ulogic

9   );

10 end entity;

12 architecture beh of mux_41 is

13 begin

14   process begin

15     case c is

16       when '0' & '0' => o <= i(0);

17       when '0' & '1' => o <= i(1);

18       when '1' & '0' => o <= i(2);

19       when '1' & '1' => o <= i(3);

20       when others      => null;

21     end case;

22     wait;

23   end process;

24 end architecture;

```

# Example: Multiplexer

HWMod

WS25

Beh. Mod.

Introduction

About

Example

Sensitivity

Process Simulation

Variables

Remarks

```

4 entity mux_41 is

5   port (

6     c : in  std_ulogic_vector(1 downto 0);

7     i : in  std_ulogic_vector(3 downto 0);

8     o : out std_ulogic

9   );

10 end entity;

12 architecture beh of mux_41 is

13 begin

14   process begin

15     case c is

16       when '0' & '0' => o <= i(0);

17       when '0' & '1' => o <= i(1);

18       when '1' & '0' => o <= i(2);

19       when '1' & '1' => o <= i(3);

20       when others      => null;

21     end case;

22     wait;      ⇒ “Termination” of circuit?!

23   end process;

24 end architecture;

```

- “Termination” of circuit not sensible

- Stays active as long as powered

- “Termination” of circuit not sensible

- Stays active as long as powered

- Instead: Model circuit as “sequential routine” for input changes

# *wait on* Statement

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

wait on

Sensitivity List

all keyword

Process Simulation

Variables

Remarks

- “Termination” of circuit not sensible

- Stays active as long as powered

- Instead: Model circuit as “sequential routine” for input changes

⇒ `wait on sensitivity_list`

- “Termination” of circuit not sensible

- Stays active as long as powered

- Instead: Model circuit as “sequential routine” for input changes

- ⇒ `wait on sensitivity_list`

- Last element in **synthesizable** process (like `wait`)

- “Termination” of circuit not sensible

- Stays active as long as powered

- Instead: Model circuit as “sequential routine” for input changes

⇒ `wait on sensitivity_list`

- Last element in **synthesizable** process (like `wait`)

- Process suspended when reaching `wait on` statement

- “Termination” of circuit not sensible

- Stays active as long as powered

- Instead: Model circuit as “sequential routine” for input changes

⇒ `wait on sensitivity_list`

- Last element in **synthesizable** process (like `wait`)

- Process suspended when reaching `wait on` statement

- Starts from top when signal in list changes

# wait on Statement

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

wait on

Sensitivity List

all keyword

Process Simulation

Variables

Remarks

- “Termination” of circuit not sensible

- Stays active as long as powered

- Instead: Model circuit as “sequential routine” for input changes

⇒ `wait on sensitivity_list`

- Last element in **synthesizable** process (like `wait`)

- Process suspended when reaching `wait on` statement

- Starts from top when signal in list changes

```

1 process begin

2   case c is

3     when false & false => o <= i(0);

4     [...]

5   end case;

6   wait on c, i;

7 end process;

```

# wait on Statement

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

wait on

Sensitivity List

all keyword

Process Simulation

Variables

Remarks

- “Termination” of circuit not sensible

- Stays active as long as powered

- Instead: Model circuit as “sequential routine” for input changes

⇒ `wait on sensitivity_list`

- Last element in **synthesizable** process (like `wait`)

- Process suspended when reaching `wait on` statement

- Starts from top when signal in list changes

```

1 process begin

2   case c is

3     when false & false => o <= i(0);

4     [...]

5   end case;

6   wait on c, i;  ← Sensitivity List

7 end process;

```

# wait on Statement

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

wait on

Sensitivity List

all keyword

Process Simulation

Variables

Remarks

- “Termination” of circuit not sensible

- Stays active as long as powered

- Instead: Model circuit as “sequential routine” for input changes

⇒ `wait on sensitivity_list`

- Last element in **synthesizable** process (like `wait`)

- Process suspended when reaching `wait on` statement

- Starts from top when signal in list changes

```

1 process begin

2   case c is

3     when false & false => o <= i(0);

4     [...]

5   end case;

6   wait on c, i;           ← Sensitivity List

7 end process;

```

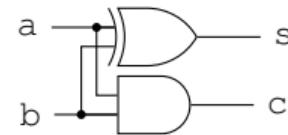

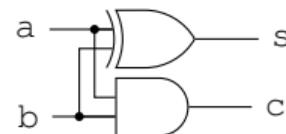

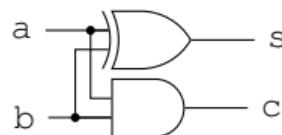

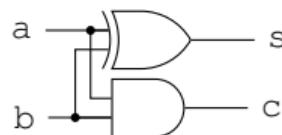

# Example: Half-adder

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

wait on

Sensitivity List

all keyword

Process Simulation

Variables

Remarks

Completeness of sensitivity list matters!

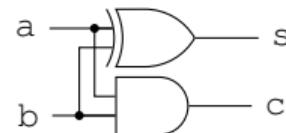

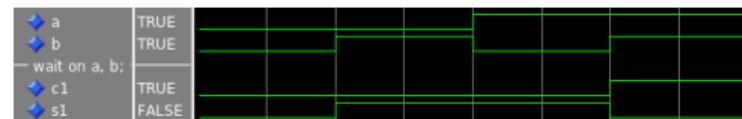

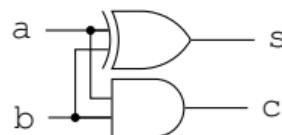

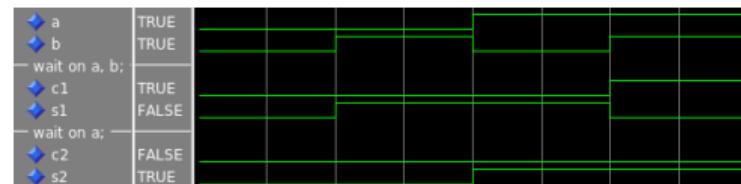

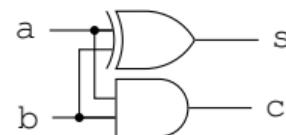

# Example: Half-adder

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

wait on

Sensitivity List

all keyword

Process Simulation

Variables

Remarks

```

1 entity ha is

2   port (

3     a, b : in boolean;

4     s, c : out boolean

5   );

6 end entity;

```

# Example: Half-adder

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

wait on

Sensitivity List

all keyword

Process Simulation

Variables

Remarks

```

1 entity ha is

2 port (

3   a, b : in boolean;

4   s, c : out boolean

5 );

6 end entity;

1 architecture arch1 of ha is

2 begin

3   process begin

4     s <= a xor b;

5     c <= a and b;

6     wait on a, b;

7   end process;

8 end architecture;

```

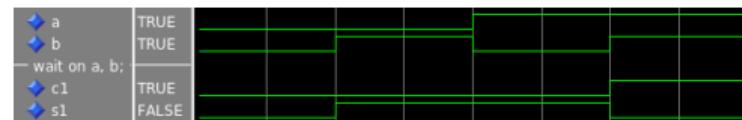

# Example: Half-adder

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

wait on

Sensitivity List

all keyword

Process Simulation

Variables

Remarks

```

1 entity ha is

2 port (

3   a, b : in boolean;

4   s, c : out boolean

5 );

6 end entity;

1 architecture arch1 of ha is

2 begin

3   process begin

4     s <= a xor b;

5     c <= a and b;

6     wait on a, b;

7   end process;

8 end architecture;

```

# Example: Half-adder

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

wait on

Sensitivity List

all keyword

Process Simulation

Variables

Remarks

```

1 entity ha is

2 port (

3   a, b : in boolean;

4   s, c : out boolean

5 );

6 end entity;

1 architecture arch1 of ha is

2 begin

3   process begin

4     s <= a xor b;

5     c <= a and b;

6     wait on a, b;

7   end process;

8 end architecture;

```

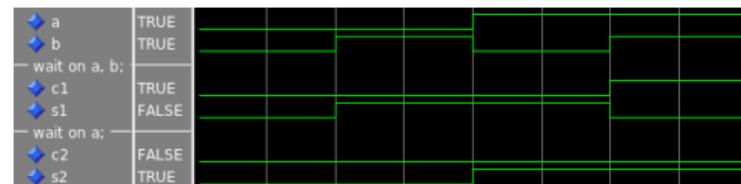

# Example: Half-adder

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

wait on

Sensitivity List

all keyword

Process Simulation

Variables

Remarks

```

1 entity ha is

2 port (

3   a, b : in boolean;

4   s, c : out boolean

5 );

6 end entity;

1 architecture arch2 of ha is

2 begin

3   process begin

4     s <= a xor b;

5     c <= a and b;

6     wait on a;

7   end process;

8 end architecture;

```

# Example: Half-adder

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

wait on

Sensitivity List

all keyword

Process Simulation

Variables

Remarks

```

1 entity ha is

2 port (

3   a, b : in boolean;

4   s, c : out boolean

5 );

6 end entity;

1 architecture arch2 of ha is

2 begin

3   process begin

4     s <= a xor b;

5     c <= a and b;

6     wait on a;

7   end process;

8 end architecture;

```

# Example: Half-adder

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

wait on

Sensitivity List

all keyword

Process Simulation

Variables

Remarks

```

1 entity ha is

2 port (

3   a, b : in boolean;

4   s, c : out boolean

5 );

6 end entity;

1 architecture arch2 of ha is

2 begin

3   process begin

4     s <= a xor b;

5     c <= a and b;

6     wait on a;

7   end process;

8 end architecture;

```

# Sensitivity List

202

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

wait on

**Sensitivity List**

all keyword

Process Simulation

Variables

Remarks

# Sensitivity List

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

wait on

Sensitivity List

all keyword

Process Simulation

Variables

Remarks

- Use sensitivity list in process declaration

- Implicit `wait on`  $\Rightarrow$  semantically equivalent

# Sensitivity List

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

wait on

Sensitivity List

all keyword

Process Simulation

Variables

Remarks

- Use sensitivity list in process declaration

- Implicit `wait on` ⇒ semantically equivalent

```

1 process (a, b)

2 begin

3   [...]

4 end process;

```

# Sensitivity List

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

wait on

Sensitivity List

all keyword

Process Simulation

Variables

Remarks

- Use sensitivity list in process declaration

- Implicit `wait on` ⇒ semantically equivalent

```

1 process (a, b)

2 begin

3 [...]

4 end process;

```

```

1 process

2 begin

3 [...]

4 wait on a, b;

5 end process;

```

# Sensitivity List

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

wait on

Sensitivity List

all keyword

Process Simulation

Variables

Remarks

- Use sensitivity list in process declaration

- Implicit `wait on` ⇒ semantically equivalent

```

1 process (a, b)

2 begin

3 [...]

4 end process;

```

```

1 process

2 begin

3 [...]

4 wait on a, b;

5 end process;

```

- No wait statements in process (sim. only)

# Sensitivity List

- Use sensitivity list in process declaration

- Implicit `wait on` ⇒ semantically equivalent

```

1 process (a, b)

2 begin

3 [...]

4 end process;

```

```

1 process

2 begin

3 [...]

4 wait on a, b;

5 end process;

```

- No wait statements in process (sim. only)

- Explicit sensitivity list for combinational logic can be

# Sensitivity List

- Use sensitivity list in process declaration

- Implicit `wait on` ⇒ semantically equivalent

```

1 process (a, b)

2 begin

3 [...]

4 end process;

```

```

1 process

2 begin

3 [...]

4 wait on a, b;

5 end process;

```

- No wait statements in process (sim. only)

- Explicit sensitivity list for combinational logic can be

- error-prone

# Sensitivity List

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

wait on

Sensitivity List

all keyword

Process Simulation

Variables

Remarks

- Use sensitivity list in process declaration

- Implicit `wait on` ⇒ semantically equivalent

```

1 process (a, b)

2 begin

3 [...]

4 end process;

```

```

1 process

2 begin

3 [...]

4 wait on a, b;

5 end process;

```

- No wait statements in process (sim. only)

- Explicit sensitivity list for combinational logic can be

- error-prone

- hard to maintain

# Sensitivity List

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

wait on

Sensitivity List

all keyword

Process Simulation

Variables

Remarks

- Use sensitivity list in process declaration

- Implicit `wait on` ⇒ semantically equivalent

```

1 process (a, b)

2 begin

3 [...]

4 end process;

```

```

1 process

2 begin

3 [...]

4 wait on a, b;

5 end process;

```

- No wait statements in process (sim. only)

- Explicit sensitivity list for combinational logic can be

- error-prone

- hard to maintain

⇒ `all` keyword for sensitivity lists

# Sensitivity Lists Using *all*

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

wait on

Sensitivity List

all keyword

Process Simulation

Variables

Remarks

- Sensitivity list is constructed at compile-time

- Consider all statements inside the process

- Apply rules to determine sensitive signals

# Sensitivity Lists Using *all*

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

wait on

Sensitivity List

all keyword

Process Simulation

Variables

Remarks

- Sensitivity list is constructed at compile-time

- Consider all statements inside the process

- Apply rules to determine sensitive signals

```

1 process (all)

2 begin

3 [...]

4 end process;

```

```

1 process (c, i)

2 begin

3 [...]

4 end process;

```

# Sensitivity Lists Using *all*

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

wait on

Sensitivity List

all keyword

Process Simulation

Variables

Remarks

- Sensitivity list is constructed at compile-time

- Consider all statements inside the process

- Apply rules to determine sensitive signals

```

1 process (all)      1 process (c, i)

2 begin             2 begin

3 [...]             3 [...]

4 end process;      4 end process;

```

- **Caveat:** Some circuits should not change for *any* input change

# Sensitivity Lists Using *all*

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

wait on

Sensitivity List

all keyword

Process Simulation

Variables

Remarks

- Sensitivity list is constructed at compile-time

- Consider all statements inside the process

- Apply rules to determine sensitive signals

```

1 process (all)           1 process (c, i)

2 begin                  2 begin

3 [...]                   3 [...]

4 end process;           4 end process;

```

- **Caveat:** Some circuits should not change for *any* input change

- Synchronous logic **only** sensitive to clock and reset

- More on that in chapter II

# Sensitivity Lists Using *all*

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

wait on

Sensitivity List

all keyword

Process Simulation

Variables

Remarks

- Sensitivity list is constructed at compile-time

- Consider all statements inside the process

- Apply rules to determine sensitive signals

```

1 process (all)          1 process (c, i)

2 begin                  2 begin

3 [...]                  3 [...]

4 end process;          4 end process;

```

- **Caveat:** Some circuits should not change for *any* input change

- Synchronous logic **only** sensitive to clock and reset

- More on that in chapter II

- Rule of thumb: Use *all* for comb. processes

# Process Simulation

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

**Process Simulation**

Example

Observations

Variables

Remarks

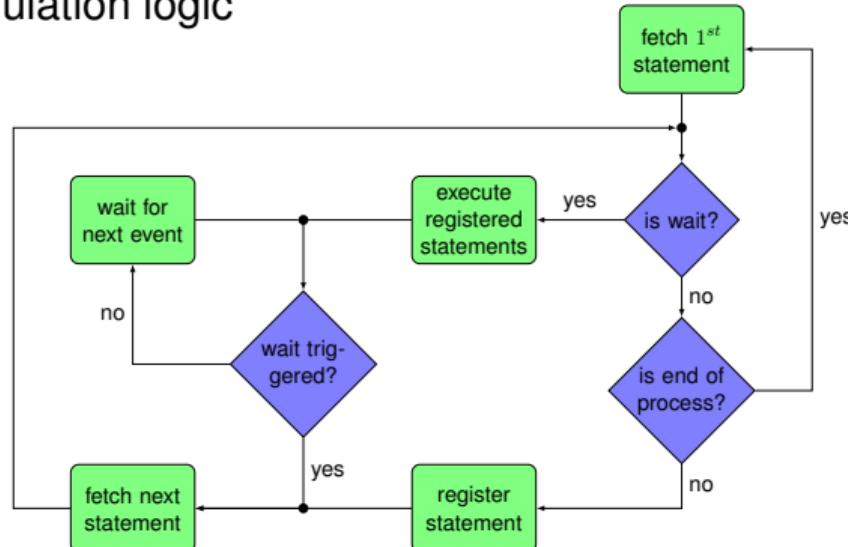

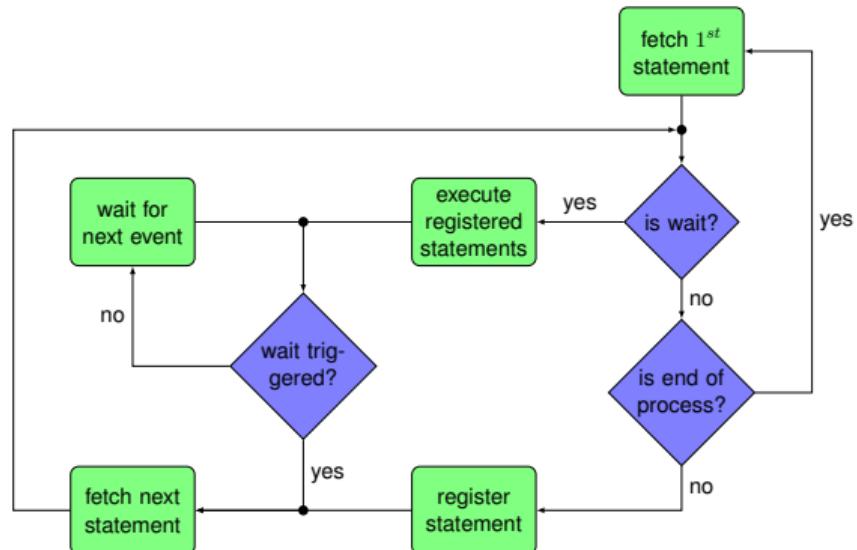

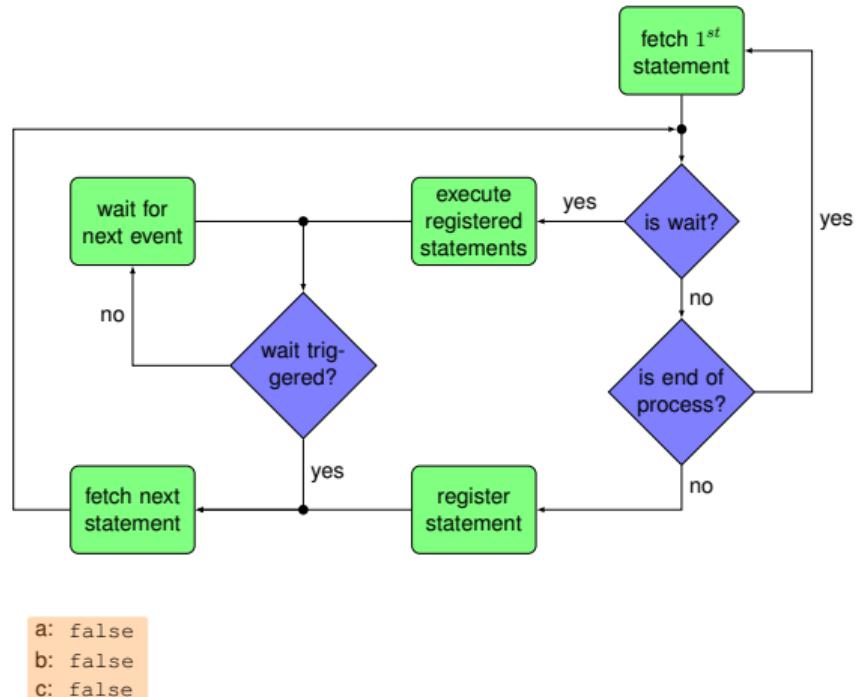

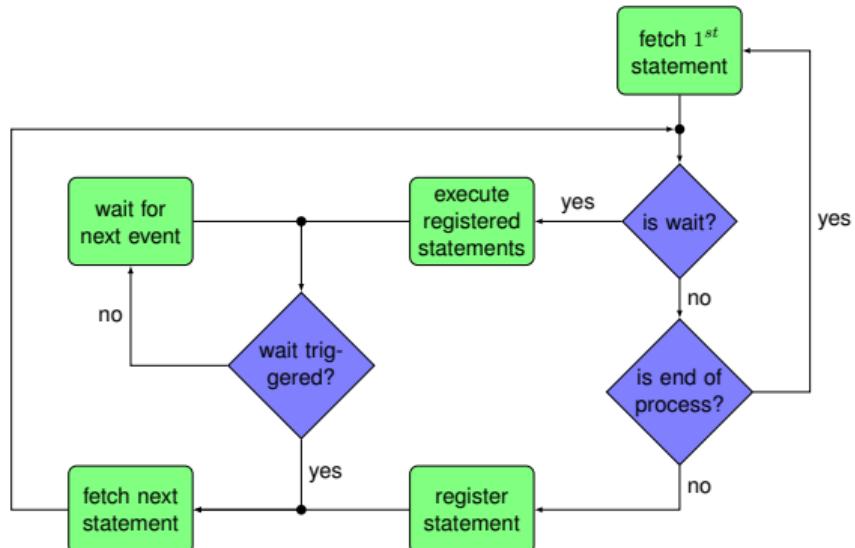

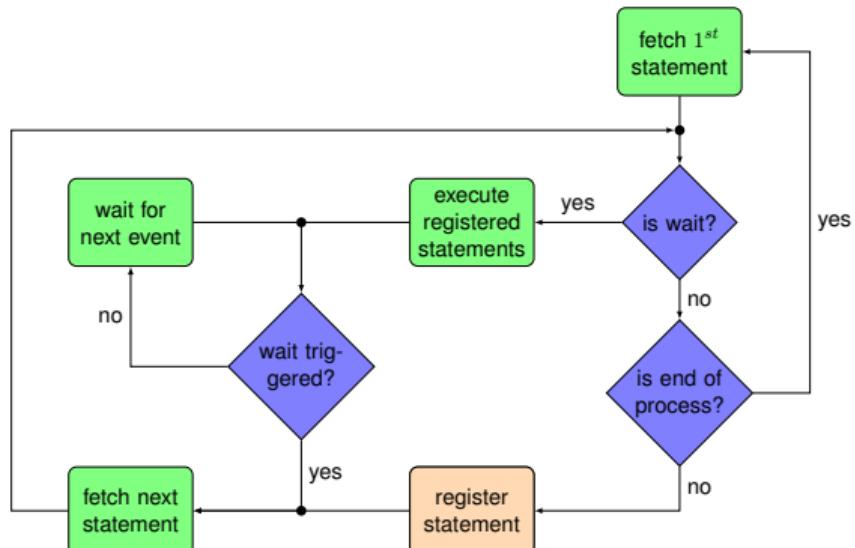

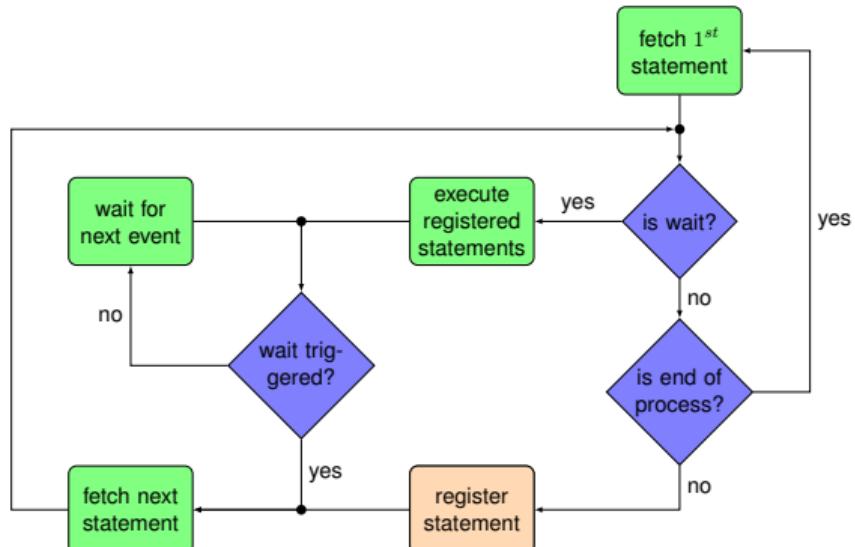

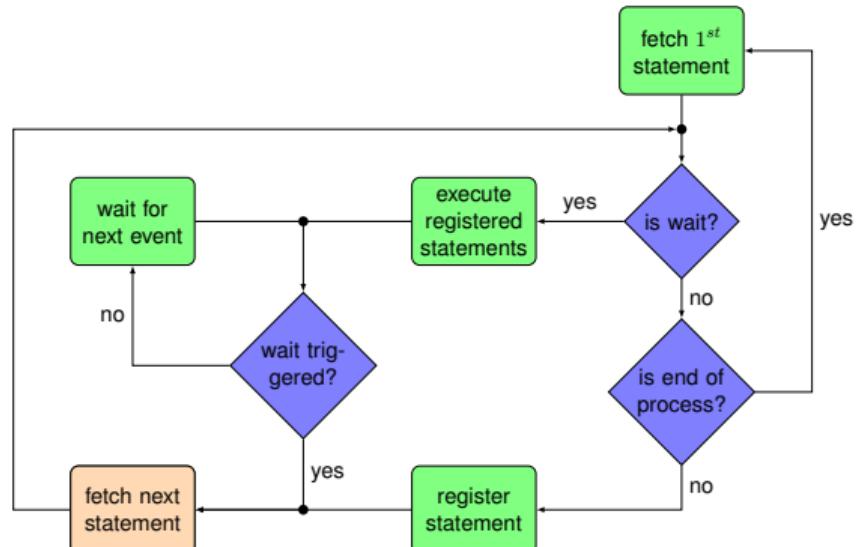

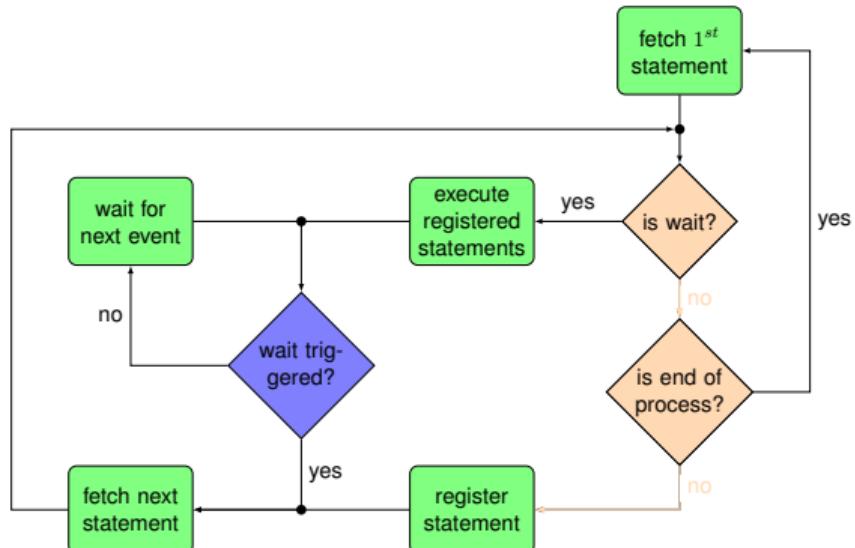

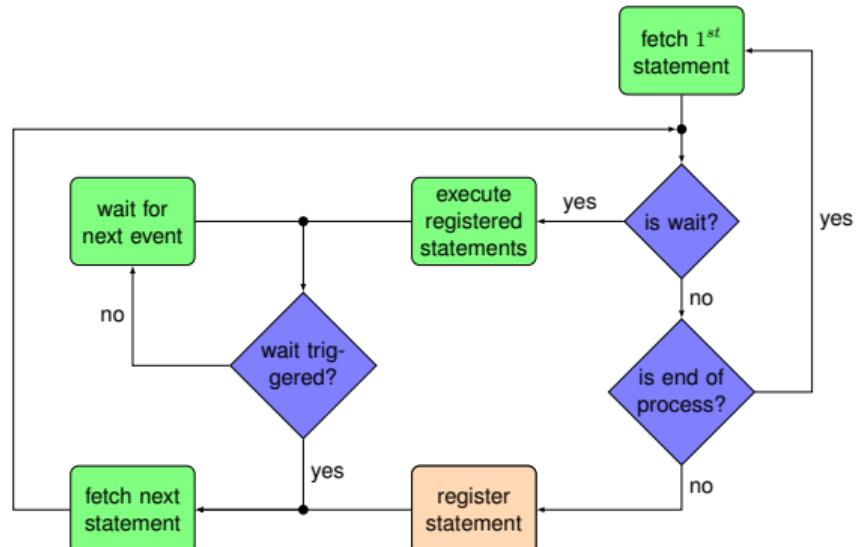

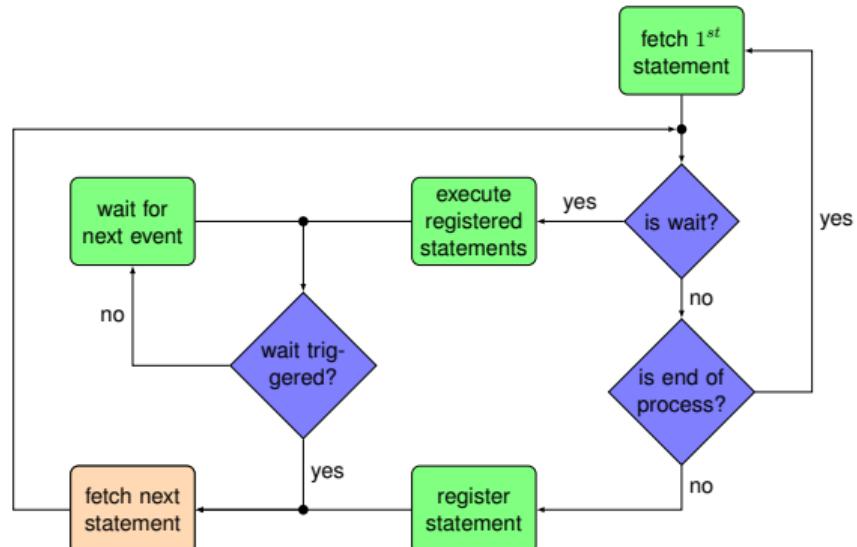

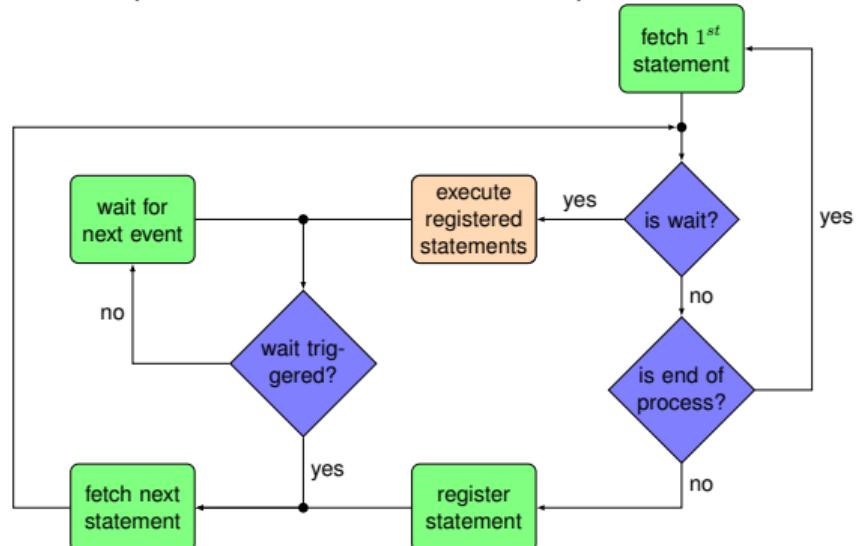

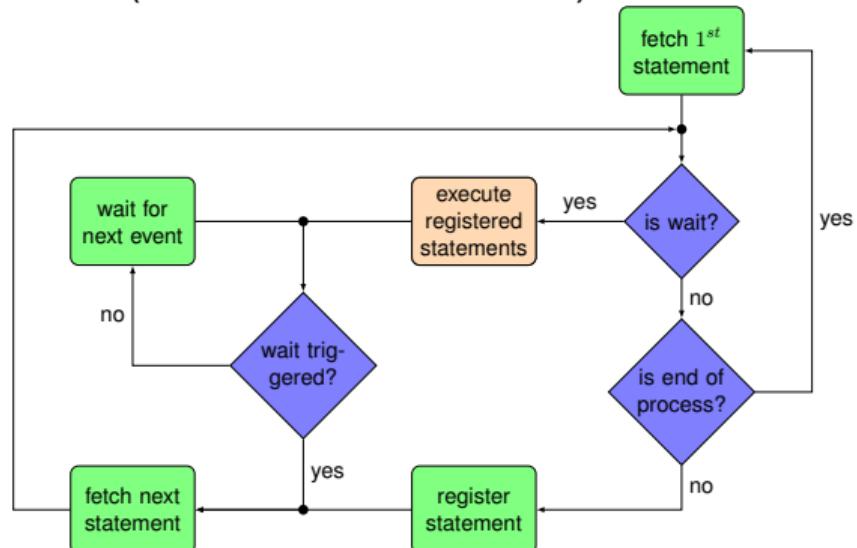

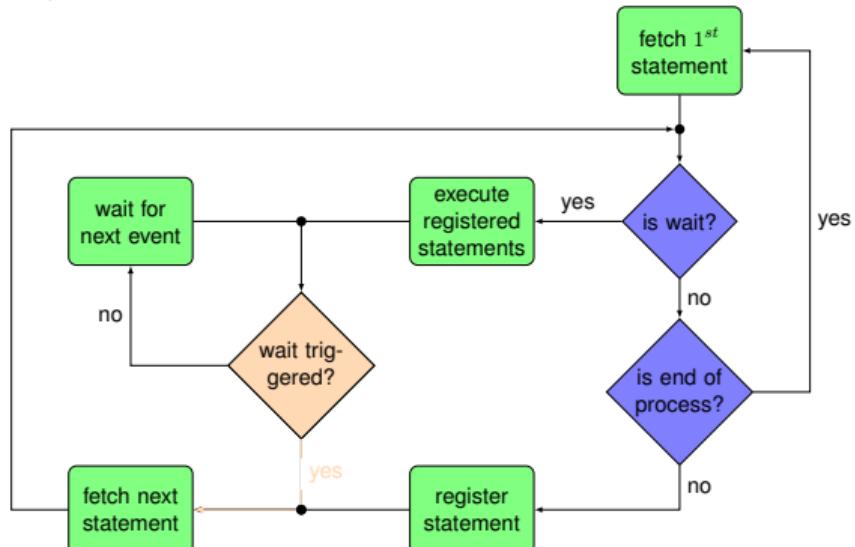

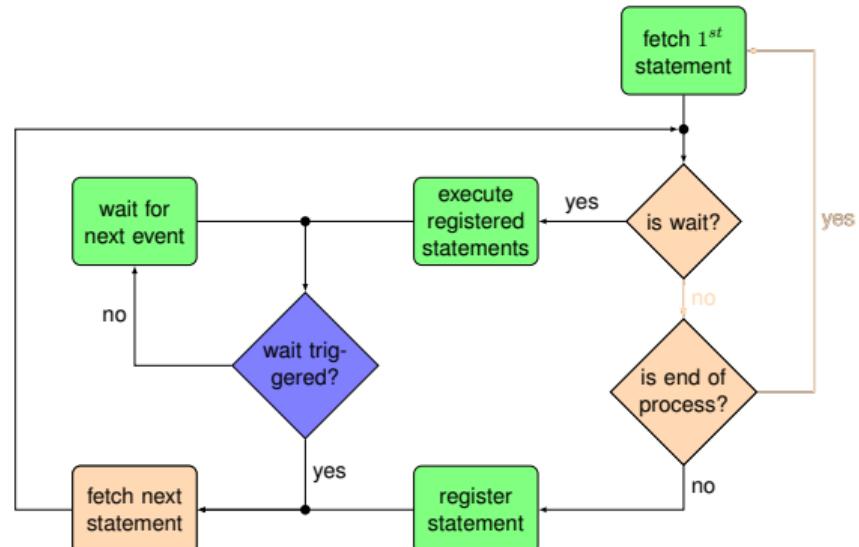

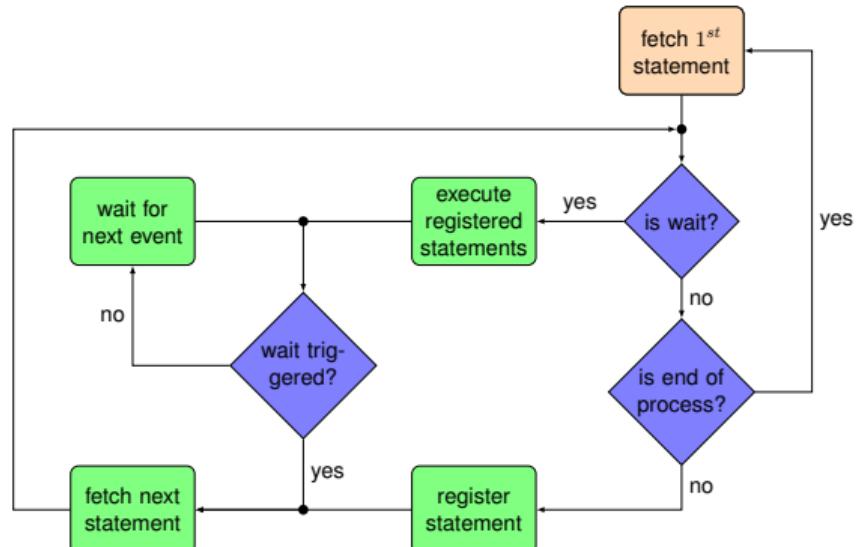

- Process is a *sequential* description

- Hardware is highly concurrent

# Process Simulation

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

**Process Simulation**

Example

Observations

Variables

Remarks

- Process is a *sequential* description

- Hardware is highly concurrent

- What does the simulator do?

# Process Simulation

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Example

Observations

Variables

Remarks

- Process is a *sequential* description

- Hardware is highly concurrent

- What does the simulator do?

⇒ Process simulation logic

# Example: Process Simulation

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Example

Observations

Variables

Remarks

```

1 architecture beh of abc is

2   signal a, b, c : boolean;

3 begin

4   process

5     begin

6       b <= a;

7       c <= b;

8       wait on a, b;

9     end process;

10 end architecture;

```

# Example: Process Simulation

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Example

Observations

Variables

Remarks

```

1 architecture beh of abc is

2   signal a, b, c : boolean;

3 begin

4   process

5     begin

6       b <= a;

7       c <= b;

8       wait on a, b;

9     end process;

10 end architecture;

```

# Example: Process Simulation

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Example

Observations

Variables

Remarks

```

1 architecture beh of abc is

2   signal a, b, c : boolean;

3 begin

4   process

5     begin

6       b <= a;

7       c <= b;

8       wait on a, b;

9     end process;

10 end architecture;

```

# Example: Process Simulation

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Example

Observations

Variables

Remarks

```

1 architecture beh of abc is

2   signal a, b, c : boolean;

3 begin

4   process

5     begin

6       b <= a;

7       c <= b;

8       wait on a, b;

9     end process;

10 end architecture;

```

# Example: Process Simulation

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Example

Observations

Variables

Remarks

```

1 architecture beh of abc is

2   signal a, b, c : boolean;

3 begin

4   process

5     begin

6       b <= a;

7       c <= b;

8       wait on a, b;

9     end process;

10 end architecture;

```

Input a changes

a: false → true

b: false

c: false

# Example: Process Simulation

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Example

Observations

Variables

Remarks

```

1 architecture beh of abc is

2   signal a, b, c : boolean;

3 begin

4   process

5     begin

6       b <= a;

7       c <= b;

8       wait on a, b;

9     end process;

10 end architecture;

```

Fetch first statement of the process body

a: true

b: false

c: false

# Example: Process Simulation

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Example

Observations

Variables

Remarks

```

1 architecture beh of abc is

2   signal a, b, c : boolean;

3 begin

4   process

5     begin

6       b <= a;

7       c <= b;

8       wait on a, b;

9     end process;

10 end architecture;

```

Neither `wait` nor `end process`

a: true

b: false

c: false

# Example: Process Simulation

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Example

Observations

Variables

Remarks

```

1 architecture beh of abc is

2   signal a, b, c : boolean;

3 begin

4   process

5     begin

6       b <= a;

7       c <= b;

8       wait on a, b;

9     end process;

10 end architecture;

```

a: true

b: false

c: false

Registered: b <= true;

# Example: Process Simulation

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Example

Observations

Variables

Remarks

```

1 architecture beh of abc is

2   signal a, b, c : boolean;

3 begin

4   process

5     begin

6       b <= a;

7       c <= b;

8       wait on a, b;

9     end process;

10 end architecture;

```

a: true

b: false

c: false

Registered: b <= true;

# Example: Process Simulation

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Example

Observations

Variables

Remarks

```

1 architecture beh of abc is

2   signal a, b, c : boolean;

3 begin

4   process

5     begin

6       b <= a;

7       c <= b;

8       wait on a, b;

9     end process;

10 end architecture;

```

## Fetch the next statement

a: true

b: false

c: false

Registered: b <= true;

# Example: Process Simulation

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Example

Observations

Variables

Remarks

```

1 architecture beh of abc is

2   signal a, b, c : boolean;

3 begin

4   process

5     begin

6       b <= a;

7       c <= b;

8       wait on a, b;

9     end process;

10 end architecture;

```

Continue until `wait` nor `end process` encountered

a: true

b: false

c: false

Registered: b <= true;

# Example: Process Simulation

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Example

Observations

Variables

Remarks

```

1 architecture beh of abc is

2   signal a, b, c : boolean;

3 begin

4   process

5     begin

6       b <= a;

7       c <= b;

8       wait on a, b;

9     end process;

10 end architecture;

```

Continue until `wait` nor `end process` encountered

a: true

b: false

c: false

Registered: b <= true;

c <= false;

# Example: Process Simulation

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Example

Observations

Variables

Remarks

```

1 architecture beh of abc is

2   signal a, b, c : boolean;

3 begin

4   process

5     begin

6       b <= a;

7       c <= b;

8       wait on a, b;

9     end process;

10 end architecture;

```

Continue until `wait` nor `end process` encountered

a: true

b: false

c: false

Registered: b <= true;

c <= false;

# Example: Process Simulation

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Example

Observations

Variables

Remarks

```

1 architecture beh of abc is

2   signal a, b, c : boolean;

3 begin

4   process

5     begin

6       b <= a;

7       c <= b;

8       wait on a, b;

9     end process;

10 end architecture;

```

wait statement encountered

a: true

b: false

c: false

Registered: b <= true;

c <= false;

# Example: Process Simulation

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Example

Observations

Variables

Remarks

```

1 architecture beh of abc is

2   signal a, b, c : boolean;

3 begin

4   process

5     begin

6       b <= a;

7       c <= b;

8       wait on a, b;

9     end process;

10 end architecture;

```

Now execute **all** registered statements (in zero simulation time)

a: true

b: false → true

c: false

Registered: b <= true;

c <= false;

# Example: Process Simulation

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Example

Observations

Variables

Remarks

```

1 architecture beh of abc is

2   signal a, b, c : boolean;

3 begin

4   process

5     begin

6       b <= a;

7       c <= b;

8       wait on a, b;

9     end process;

10 end architecture;

```

Now execute **all** registered statements (in zero simulation time)

a: true

b: true

c: false → false

Registered: c <= false;

# Example: Process Simulation

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Example

Observations

Variables

Remarks

```

1 architecture beh of abc is

2   signal a, b, c : boolean;

3 begin

4   process

5     begin

6       b <= a;

7       c <= b;

8       wait on a, b;

9     end process;

10 end architecture;

```

Change of b triggered `wait on a, b`

a: true

b: true

c: false

Registered:

# Example: Process Simulation

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Example

Observations

Variables

Remarks

```

1 architecture beh of abc is

2   signal a, b, c : boolean;

3 begin

4   process

5     begin

6       b <= a;

7       c <= b;

8       wait on a, b;

9     end process;

10 end architecture;

```

## Fetch next statement

a: true

b: true

c: false

Registered:

# Example: Process Simulation

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Example

Observations

Variables

Remarks

```

1 architecture beh of abc is

2   signal a, b, c : boolean;

3 begin

4   process

5     begin

6       b <= a;

7       c <= b;

8       wait on a, b;

9     end process;

10 end architecture;

```

End of process  $\Rightarrow$  Repeat

a: true

b: true

c: false

Registered:

# Observations: Process Simulation

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Example

Observations

Variables

Remarks

## Observation I

Statements are not executed immediately, but rather gathered until a wait is encountered. Then they are all executed without consuming simulation time. This mimics a concurrent execution.

# Observations: Process Simulation

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Example

Observations

Variables

Remarks

## Observation I

Statements are not executed immediately, but rather gathered until a wait is encountered. Then they are all executed without consuming simulation time. This mimics a concurrent execution.

## Observation II

Without `b` in the sensitivity list in the example, `c` would end remaining `false` until the next change of `a`  $\Rightarrow$  proper sensitivity list paramount.

# Observations: Process Simulation

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Example

Observations

Variables

Remarks

## Observation I

Statements are not executed immediately, but rather gathered until a wait is encountered. Then they are all executed without consuming simulation time. This mimics a concurrent execution.

## Observation II

Without `b` in the sensitivity list in the example, `c` would end remaining `false` until the next change of `a`  $\Rightarrow$  proper sensitivity list paramount.

## Observation III

A process without (implicit) `wait` statement loops endlessly.

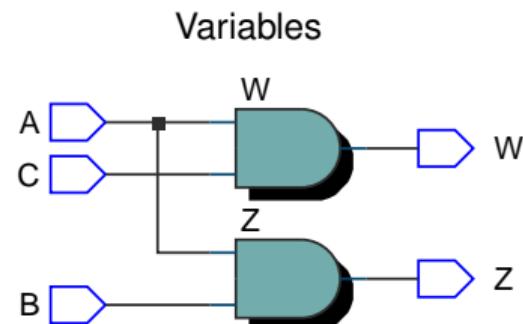

# Variables

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Variables

Example

Remarks

- Signal assignments executed at `wait`

# Variables

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Variables

Example

Remarks

- Signal assignments executed at `wait`

⇒ Variables

# Variables

- Signal assignments executed at `wait`

⇒ Variables

- In process declarative part

```

variable x : integer := 10;

```

- Signal assignments executed at `wait`

- ⇒ Variables

- In process declarative part

```

variable x : integer := 10;

```

- Assignments (`:=`) have *immediate* effect

# Variables

- Signal assignments executed at `wait`

⇒ Variables

- In process declarative part

```

variable x : integer := 10;

```

- Assignments (`:=`) have *immediate* effect

- **Not** in sensitivity list

- Signal assignments executed at `wait`

- ⇒ Variables

- In process declarative part

```

variable x : integer := 10;

```

- Assignments (`:=`) have *immediate* effect

- **Not** in sensitivity list

- Name and reuse intermediate expressions

- Signal assignments executed at `wait`

⇒ Variables

## ■ In process declarative part

```

variable x : integer := 10;

```

- Assignments (`:=`) have *immediate* effect

- **Not** in sensitivity list

- Name and reuse intermediate expression

## ■ Example

```

1 entity wide_and is

2 port(

3   i : in std_ulogic_vector;

4   o : out std_ulogic

5 );

6

7   process (all) is

8   variable result : std_ulogic := '1';

9   begin

10    for x in i'range loop

11      result := result and i(x);

12    end loop;

13    o <= result;

14  end process;

15

16 end wide_and;

```

# Variables

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Variables

Example

Remarks

- Signal assignments executed at `wait`

⇒ Variables

- In process declarative part

```

variable x : integer := 10;

```

- Assignments (`:=`) have *immediate* effect

- **Not** in sensitivity list

- Name and reuse intermediate expressions

- Example

```

1 entity wide_and is

2 port(

3   i : in std_ulogic_vector;

4   o : out std_ulogic

5 );

```

```

1 process (all) is

2   variable result : std_ulogic := '1';

3 begin

4   for x in i'range loop

5     result := result and i(x);

6   end loop;

7   o <= result;

8 end process;

```

# Example: Variables vs Signals

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Variables

**Example**

Remarks

# Example: Variables vs Signals

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Variables

**Example**

Remarks

```

1 architecture sig of app is

2   signal w, x, y, z : std_ulogic;

3 begin

4   process (all) begin

5     x <= a;

6     y <= b;

7     z <= x and y;

8     y <= c;

9     w <= x and y;

10  end process;

11 end architecture;

```

# Example: Variables vs Signals

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Variables

Example

Remarks

```

1 architecture sig of app is

2   signal w, x, y, z : std_ulogic;

3 begin

4   process (all) begin

5     x <= a;

6     y <= b;

7     z <= x and y;

8     y <= c;

9     w <= x and y;

10  end process;

11 end architecture;

```

Initial Values: A=B=C=W=X=Y=Z='1', C='1' → '0'

# Example: Variables vs Signals

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Variables

Example

Remarks

```

1 architecture sig of app is

2   signal w, x, y, z : std_ulogic;

3 begin

4   process (all) begin

5     x <= a;

6     y <= b;

7     z <= x and y;

8     y <= c;

9     w <= x and y;

10  end process;

11 end architecture;

```

Initial Values: A=B=C=W=X=Y=Z='1', C='1' → '0'

# Example: Variables vs Signals

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Variables

Example

Remarks

```

1 architecture sig of app is

2   signal w, x, y, z : std_ulogic;

3 begin

4   process (all) begin

5     x <= a;

6     y <= b;

7     z <= x and y;

8     y <= c;

9     w <= x and y;

10  end process;

11 end architecture;

```

Initial Values: A=B=C=W=X=Y=Z='1', C='1'  $\rightarrow$  '0'

| Iteration # | signal values at end |

|-------------|----------------------|

| 1           | x='1'                |

| 2           |                      |

# Example: Variables vs Signals

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Variables

Example

Remarks

```

1 architecture sig of app is

2   signal w, x, y, z : std_ulogic;

3 begin

4   process (all) begin

5     x <= a;

6     y <= b;

7     z <= x and y;

8     y <= c;

9     w <= x and y;

10  end process;

11 end architecture;

```

Initial Values: A=B=C=W=X=Y=Z='1', C='1'  $\rightarrow$  '0'

| Iteration # | signal values at end |

|-------------|----------------------|

| 1           | x='1', y='1'         |

| 2           |                      |

# Example: Variables vs Signals

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Variables

Example

Remarks

```

1 architecture sig of app is

2   signal w, x, y, z : std_ulogic;

3 begin

4   process (all) begin

5     x <= a;

6     y <= b;

7     z <= x and y; // Line 7 is highlighted

8     y <= c;

9     w <= x and y;

10  end process;

11 end architecture;

```

Initial Values: A=B=C=W=X=Y=Z='1', C='1'  $\rightarrow$  '0'

| Iteration # | signal values at end  |

|-------------|-----------------------|

| 1           | x='1', y='1'<br>z='1' |

| 2           |                       |

# Example: Variables vs Signals

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Variables

Example

Remarks

```

1 architecture sig of app is

2   signal w, x, y, z : std_ulogic;

3 begin

4   process (all) begin

5     x <= a;

6     y <= b;

7     z <= x and y;

8     y <= c;

9     w <= x and y;

10  end process;

11 end architecture;

```

Initial Values: A=B=C=W=X=Y=Z='1', C='1'  $\rightarrow$  '0'

| Iteration # | signal values at end  |

|-------------|-----------------------|

| 1           | x='1', y='0'<br>z='1' |

| 2           |                       |

# Example: Variables vs Signals

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Variables

Example

Remarks

```

1 architecture sig of app is

2   signal w, x, y, z : std_ulogic;

3 begin

4   process (all) begin

5     x <= a;

6     y <= b;

7     z <= x and y;

8     y <= c;

9     w <= x and y;

10  end process;

11 end architecture;

```

Initial Values: A=B=C=W=X=Y=Z='1', C='1'  $\rightarrow$  '0'

| Iteration # | signal values at end         |

|-------------|------------------------------|

| 1           | x='1', y='0'<br>z='1', w='1' |

| 2           |                              |

# Example: Variables vs Signals

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Variables

Example

Remarks

```

1 architecture sig of app is

2   signal w, x, y, z : std_ulogic;

3 begin

4   process (all) begin

5     x <= a;

6     y <= b;

7     z <= x and y;

8     y <= c;

9     w <= x and y;

10  end process;

11 end architecture;

```

Initial Values: A=B=C=W=X=Y=Z='1', C='1'  $\rightarrow$  '0'

| Iteration # | signal values at end         |

|-------------|------------------------------|

| 1           | x='1', y='0'<br>z='1', w='1' |

| 2           | w='0', x='1'<br>y='0', z='0' |

# Example: Variables vs Signals

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Variables

Example

Remarks

```

1 architecture sig of app is

2   signal w, x, y, z : std_ulogic;

3 begin

4   process (all) begin

5     x <= a;

6     y <= b;

7     z <= x and y;

8     y <= c;

9     w <= x and y;

10  end process;

11 end architecture;

```

```

1 architecture var of app is

2   signal w, z : std_ulogic;

3 begin

4   process (all) is

5     variable x, y : std_ulogic;

6   begin

7     x := a;

8     y := b;

9     z <= x and y;

10    y := c;

11    w <= x and y;

12  end process;

13 end architecture;

```

Initial Values: A=B=C=W=X=Y=Z='1', C='1'  $\rightarrow$  '0'

| Iteration # | signal values at end         |

|-------------|------------------------------|

| 1           | x='1', y='0'<br>z='1', w='1' |

| 2           | w='0', x='1'<br>y='0', z='0' |

# Example: Variables vs Signals

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Variables

Example

Remarks

```

1 architecture sig of app is

2   signal w, x, y, z : std_ulogic;

3 begin

4   process (all) begin

5     x <= a;

6     y <= b;

7     z <= x and y;

8     y <= c;

9     w <= x and y;

10  end process;

11 end architecture;

```

```

1 architecture var of app is

2   signal w, z : std_ulogic;

3 begin

4   process (all) is

5     variable x, y : std_ulogic;

6   begin

7     x := a;

8     y := b;

9     z <= x and y;

10    y := c;

11    w <= x and y;

12  end process;

13 end architecture;

```

Initial Values: A=B=C=W=X=Y=Z='1', C='1'  $\rightarrow$  '0'

| Iteration # | signal values at end         |

|-------------|------------------------------|

| 1           | x='1', y='0'<br>z='1', w='1' |

| 2           | w='0', x='1'<br>y='0', z='0' |

# Example: Variables vs Signals

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Variables

Example

Remarks

```

1 architecture sig of app is

2   signal w, x, y, z : std_ulogic;

3 begin

4   process (all) begin

5     x <= a;

6     y <= b;

7     z <= x and y;

8     y <= c;

9     w <= x and y;

10  end process;

11 end architecture;

```

```

1 architecture var of app is

2   signal w, z : std_ulogic;

3 begin

4   process (all) is

5     variable x, y : std_ulogic;

6   begin

7     x := a;

8     y := b;

9     z <= x and y;

10    y := c;

11    w <= x and y;

12  end process;

13 end architecture;

```

Initial Values: A=B=C=W=X=Y=Z='1', C='1'  $\rightarrow$  '0'

| Iteration # | signal values at end         |

|-------------|------------------------------|

| 1           | x='1', y='0'<br>z='1', w='1' |

| 2           | w='0', x='1'<br>y='0', z='0' |

| Iteration # | signal values at end |

|-------------|----------------------|

| 1           |                      |

| 2           |                      |

# Example: Variables vs Signals

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Variables

Example

Remarks

```

1 architecture sig of app is

2   signal w, x, y, z : std_ulogic;

3 begin

4   process (all) begin

5     x <= a;

6     y <= b;

7     z <= x and y;

8     y <= c;

9     w <= x and y;

10  end process;

11 end architecture;

```

```

1 architecture var of app is

2   signal w, z : std_ulogic;

3 begin

4   process (all) is

5     variable x, y : std_ulogic;

6   begin

7     x := a;

8     y := b;

9     z <= x and y;

10    y := c;

11    w <= x and y;

12  end process;

13 end architecture;

```

Initial Values: A=B=C=W=X=Y=Z='1', C='1'  $\rightarrow$  '0'

| Iteration # | signal values at end         |

|-------------|------------------------------|

| 1           | x='1', y='0'<br>z='1', w='1' |

| 2           | w='0', x='1'<br>y='0', z='0' |

| Iteration # | signal values at end |

|-------------|----------------------|

| 1           | x='1', y='1'         |

| 2           |                      |

# Example: Variables vs Signals

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Variables

Example

Remarks

```

1 architecture sig of app is

2   signal w, x, y, z : std_ulogic;

3 begin

4   process (all) begin

5     x <= a;

6     y <= b;

7     z <= x and y;

8     y <= c;

9     w <= x and y;

10  end process;

11 end architecture;

```

```

1 architecture var of app is

2   signal w, z : std_ulogic;

3 begin

4   process (all) is

5     variable x, y : std_ulogic;

6   begin

7     x := a;

8     y := b;

9     z <= x and y;

10    y := c;

11    w <= x and y;

12  end process;

13 end architecture;

```

Initial Values: A=B=C=W=X=Y=Z='1', C='1'  $\rightarrow$  '0'

| Iteration # | signal values at end         |

|-------------|------------------------------|

| 1           | x='1', y='0'<br>z='1', w='1' |

| 2           | w='0', x='1'<br>y='0', z='0' |

| Iteration # | signal values at end  |

|-------------|-----------------------|

| 1           | x='1', y='1'<br>z='1' |

| 2           |                       |

# Example: Variables vs Signals

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Variables

Example

Remarks

```

1 architecture sig of app is

2   signal w, x, y, z : std_ulogic;

3 begin

4   process (all) begin

5     x <= a;

6     y <= b;

7     z <= x and y;

8     y <= c;

9     w <= x and y;

10  end process;

11 end architecture;

```

```

1 architecture var of app is

2   signal w, z : std_ulogic;

3 begin

4   process (all) is

5     variable x, y : std_ulogic;

6   begin

7     x := a;

8     y := b;

9     z <= x and y;

10    y := c;

11    w <= x and y;

12  end process;

13 end architecture;

```

Initial Values: A=B=C=W=X=Y=Z='1', C='1'  $\rightarrow$  '0'

| Iteration # | signal values at end         |

|-------------|------------------------------|

| 1           | x='1', y='0'<br>z='1', w='1' |

| 2           | w='0', x='1'<br>y='0', z='0' |

| Iteration # | signal values at end  |

|-------------|-----------------------|

| 1           | x='1', y='0'<br>z='1' |

| 2           |                       |

# Example: Variables vs Signals

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Variables

Example

Remarks

```

1 architecture sig of app is

2   signal w, x, y, z : std_ulogic;

3 begin

4   process (all) begin

5     x <= a;

6     y <= b;

7     z <= x and y;

8     y <= c;

9     w <= x and y;

10  end process;

11 end architecture;

```

```

1 architecture var of app is

2   signal w, z : std_ulogic;

3 begin

4   process (all) is

5     variable x, y : std_ulogic;

6   begin

7     x := a;

8     y := b;

9     z <= x and y;

10    y := c;

11    w <= x and y;

12  end process;

13 end architecture;

```

Initial Values: A=B=C=W=X=Y=Z='1', C='1'  $\rightarrow$  '0'

| Iteration # | signal values at end         |

|-------------|------------------------------|

| 1           | x='1', y='0'<br>z='1', w='1' |

| 2           | w='0', x='1'<br>y='0', z='0' |

| Iteration # | signal values at end         |

|-------------|------------------------------|

| 1           | x='1', y='0'<br>z='1', w='0' |

| 2           |                              |

# Example: Variables vs Signals

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Variables

Example

Remarks

```

1 architecture sig of app is

2   signal w, x, y, z : std_ulogic;

3 begin

4   process (all) begin

5     x <= a;

6     y <= b;

7     z <= x and y;

8     y <= c;

9     w <= x and y;

10  end process;

11 end architecture;

```

```

1 architecture var of app is

2   signal w, z : std_ulogic;

3 begin

4   process (all) is

5     variable x, y : std_ulogic;

6   begin

7     x := a;

8     y := b;

9     z <= x and y;

10    y := c;

11    w <= x and y;

12  end process;

13 end architecture;

```

Initial Values: A=B=C=W=X=Y=Z='1', C='1'  $\rightarrow$  '0'

| Iteration # | signal values at end         |

|-------------|------------------------------|

| 1           | x='1', y='0'<br>z='1', w='1' |

| 2           | w='0', x='1'<br>y='0', z='0' |

| Iteration # | signal values at end         |

|-------------|------------------------------|

| 1           | x='1', y='0'<br>z='1', w='0' |

| 2           | -                            |

# Example: Variables vs Signals

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Variables

Example

Remarks

```

1 architecture sig of app is

2   signal w, x, y, z : std_ulogic;

3 begin

4   process (all) begin

5     x <= a;

6     y <= b;

7     z <= x and y;

8     y <= c;

9     w <= x and y;

10  end process;

11 end architecture;

```

```

1 architecture var of app is

2   signal w, z : std_ulogic;

3 begin

4   process (all) is

5     variable y : std_ulogic;

6     begin

7       y <= x and y;

8       y := c;

9       w <= x and y;

10  end process;

11 end architecture;

```

Not the same circuit!

Initial Values: A=B=C=W=X=Y=Z='1', C='1' → '0'

| Iteration # | signal values at end         |

|-------------|------------------------------|

| 1           | x='1', y='0'<br>z='1', w='1' |

| 2           | w='0', x='1'<br>y='0', z='0' |

| Iteration # | signal values at end         |

|-------------|------------------------------|

| 1           | x='1', y='0'<br>z='1', w='0' |

| 2           | -                            |

# Variables vs Signals (Cont'd)

HWMod

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Variables

Example

Remarks

⇒ Use of **variable** and **signal** not equivalent!

# Variables vs Signals (Cont'd)

HWMOD

WS25

Beh. Mod.

Introduction

Sensitivity

Process Simulation

Variables

Example

Remarks

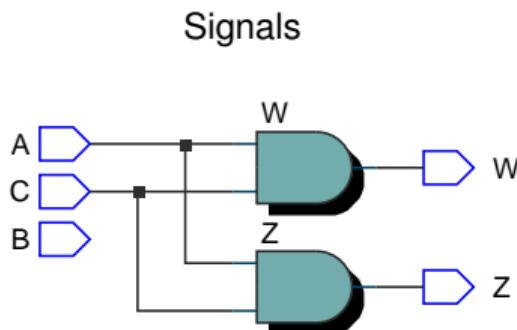

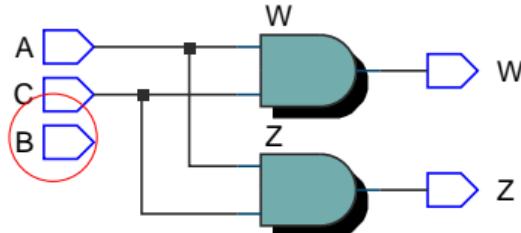

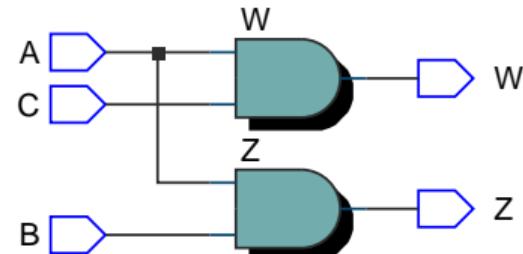

⇒ Use of **variable** and **signal** not equivalent!

Signals

Variables

## Beh. Mod.

- Introduction

- Sensitivity

- Process Simulation

- Variables

- Remarks

## ■ process declaration (simplified)

```

1 [label] : process designator [(sensitivity_list)] [is]

2   [declarative_part]

3   begin

4     [statement part] -- process body

5   end process;

```

# Remarks

## ■ process declaration (simplified)

```

1 [label] : process designator [(sensitivity_list)] [is]

2 [declarative_part]

3 begin

4 [statement part] -- process body

5 end process;

```

## ■ Every concurrent signal has an equivalent process

# Remarks

## ■ process declaration (simplified)

```

1 [label] : process designator [(sensitivity_list)] [is]

2   [declarative_part]

3   begin

4     [statement part] -- process body

5   end process;

```

## ■ Every concurrent signal has an equivalent process

- Examples: MUX41, halfadder, wide AND-gate

# Remarks

## ■ process declaration (simplified)

```

1 [label] : process designator [(sensitivity_list)] [is]

2   [declarative_part]

3   begin

4     [statement part] -- process body

5   end process;

```

## ■ Every concurrent signal has an equivalent process

- Examples: MUX41, halfadder, wide AND-gate

- The other direction is not true (e.g., sync. logic)

## ■ process declaration (simplified)

```

1 [label] : process designator [(sensitivity_list)] [is]

2   [declarative_part]

3   begin

4     [statement part] -- process body

5   end process;

```

- Every concurrent signal has an equivalent process

- Examples: MUX41, halfadder, wide AND-gate

- The other direction is not true (e.g., sync. logic)

- Arbitrary many processes possible

# Remarks

## ■ process declaration (simplified)

```

1 [label] : process designator [(sensitivity_list)] [is]

2   [declarative_part]

3   begin

4     [statement part] -- process body

5   end process;

```

- Every concurrent signal has an equivalent process

- Examples: MUX41, halfadder, wide AND-gate

- The other direction is not true (e.g., sync. logic)

- Arbitrary many processes possible

- Executed concurrently

## ■ process declaration (simplified)

```

1 [label] : process designator [(sensitivity_list)] [is]

2 [declarative_part]

3 begin

4 [statement part] -- process body

5 end process;

```

- Every concurrent signal has an equivalent process

- Examples: MUX41, halfadder, wide AND-gate

- The other direction is not true (e.g., sync. logic)

- Arbitrary many processes possible

- Executed concurrently

- Order of actual execution *undefined* ⇒ do not rely on it

# Lecture Complete!